Phase lock a VCXO to a standard 10MHz or to a GPS(1pps)

This compact circuit locks a VCXO to a reference (10MHz or other) or to 1pps (pulse per second) from a GPS receiver. It was built using programmable logic from ALTERA

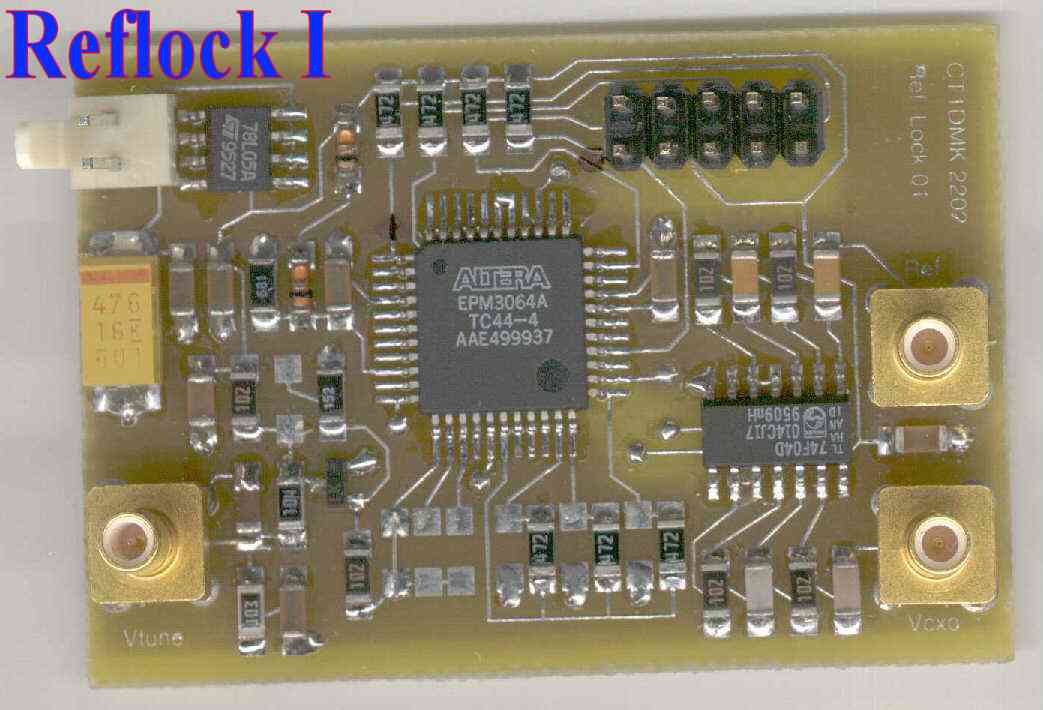

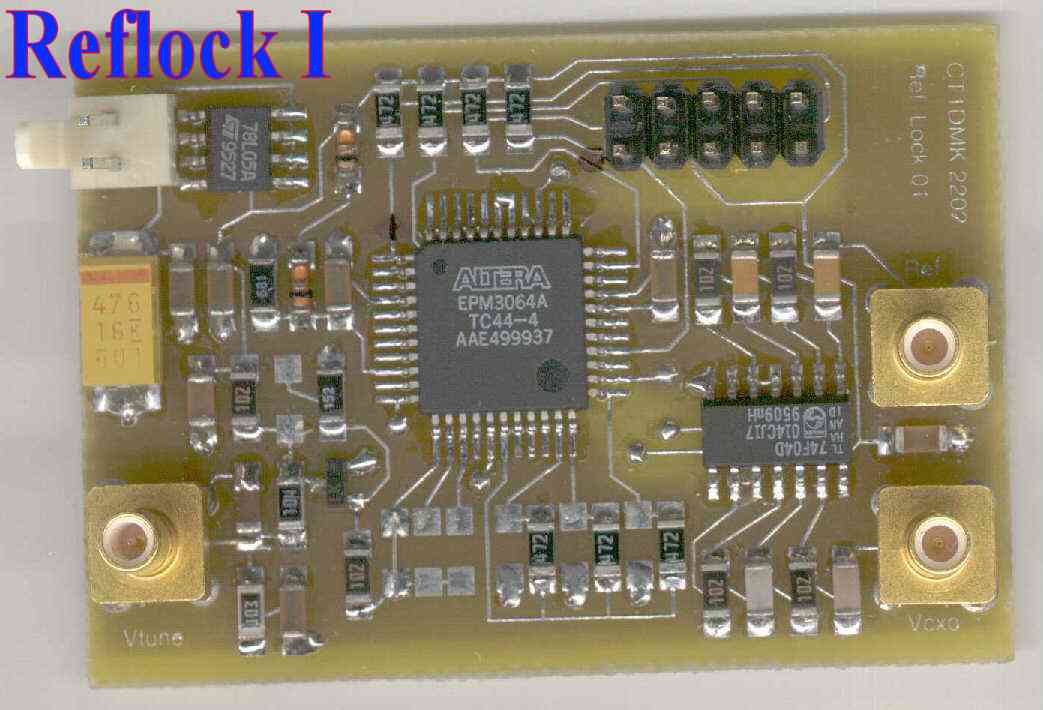

Two main versions were been designed, the REFLOCK I that is using a MAX I Altera CPLD (ref: EPM3064)

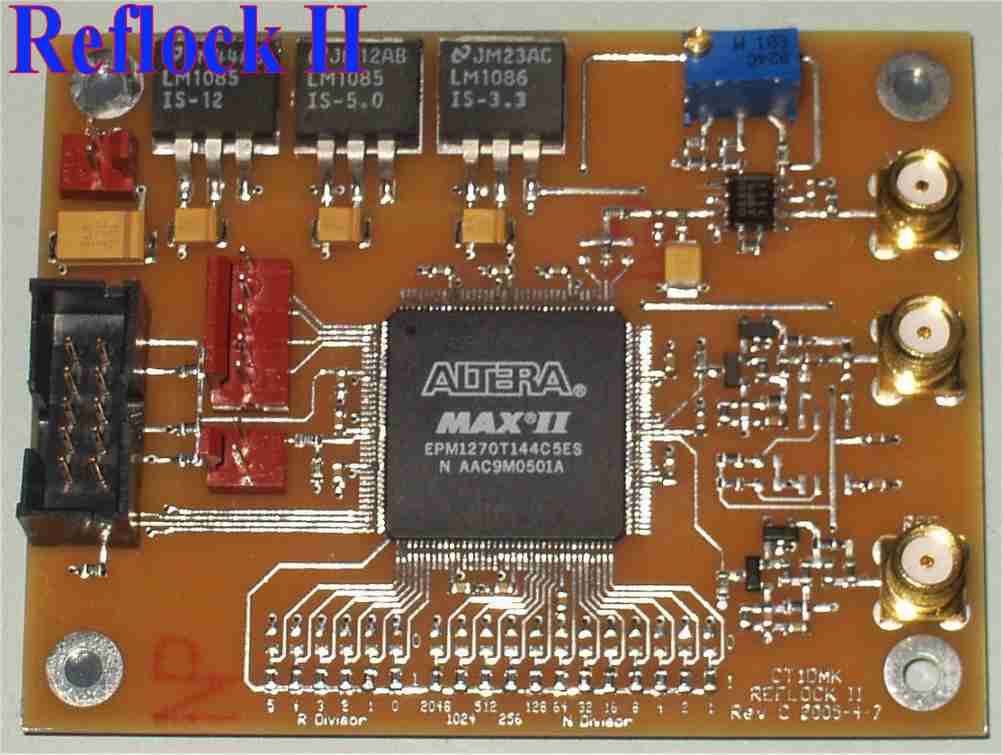

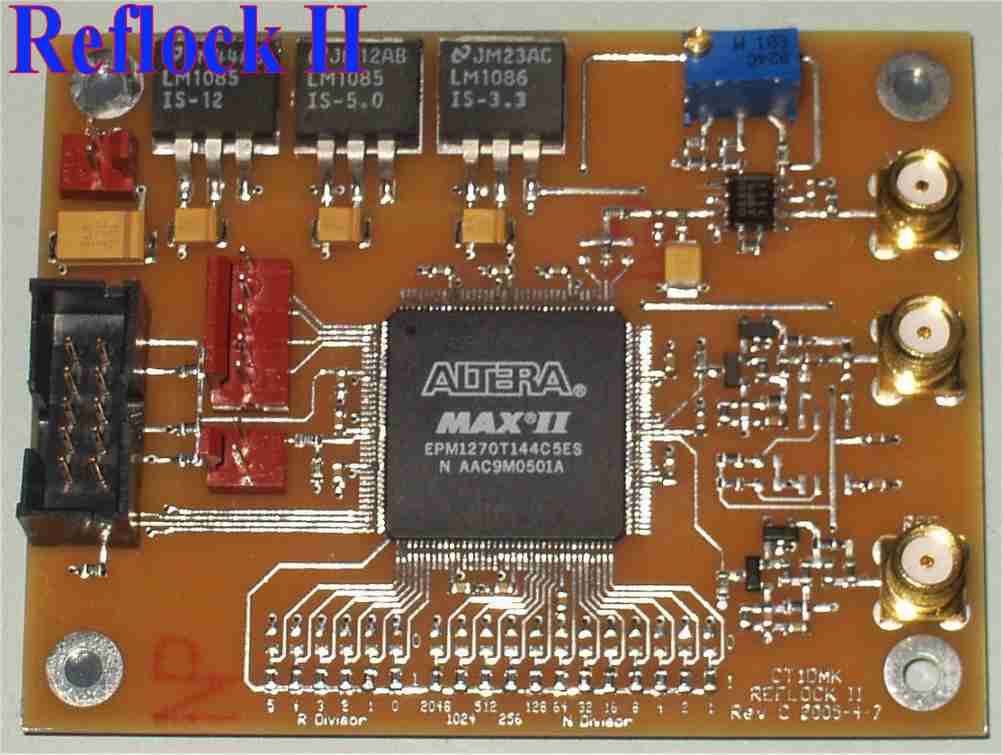

And the REFLOCK II that is using the new MAX II Altera CPLD (ref: EPM1270)Many configurations for phase lock schemes are possible, any standard PLL can be done with this circuit (any lower frequency will work just fine). Any frequency multiplier with an input in the few MHz range and an output in the 100MHz range (1GHz with reflock II) can be done, provided the correct chip configuration.

The very same PCB and electrical circuit is used for most of the REFLOCK I mutants.

Also for the REFLOCK II just one PCB design can implement a lot of different frequency locking configurations.

The REFLOCK II has much higher performance and can operate at much higher frequency.

Reflock II

This design incorporates the MaxII CPLD from Altera and has the capability of operating directly up to 250MHz with no prescaler and beyond 1GHz with the prescaler fit on the board.

The size of CPLD used now allows for enhanced resolution 1pps circuit with capability of connecting to a PIC processor (Atmel.. or whatever is your favorite) and things like lock detection and full numeric loop performance monitoring are possible. Well, and many other things that don't occur to me at the moment. This design was done in cooperation with Steven Bible N7HPR that did all diagrams and PCB design. Performance tests are being conducted by Steve N7HPR, John N8UR, Tom N8ZM and myself.

TAPR made REFLOCK II available for the people , visit TAPR web site. All documentation is being prepared right now.

Latest configuration files you will get them here on my pages.The schmatic diagrams of Reflock II. [Schematics]

The assembly and operations manual. [Manual]

Configuration files. [reflock II configurations as in Oct.2012]

If you want any of the VHDL Design files please ask on email .

Reflock I

This is the first and original reflock design intended to lock all sort of VCXOs commonly used in transverters and transceivers. Don't presume this circuit has limited capabilites for the number of frequencies available until you see the list of possible configuration that exist now. The list kept growing for many years now and contains all Xtal frequencies you may imagine, if not drop me an email and I will keep adding more Xtal frequencies to it.

The schematic diagrams [Schematics]

The PCB in PS and PDF files, Bottom, Top and Silk. [PCB files]

The PCB gerber files, Bottom, Top and solder resists. [PCB gerber files] Configuration files. [reflock I configurations as in 19 Jun 2013]

If you want any of the VHDL Design files please ask on email

. (Contains all versions, the standard and the custom made to accommodate specific requests)

Versatile Locking to 10MHz

This is a NEW extremely versatile PLL system using Binary Coded Jumpers to select VCXO, or XTAL Freq, division at both the LO & Ref Freq. It requires a slightly different PCB layout but all pins were left in the same positions as on the basic reflock design.

This New Design eliminates the many short Falls of the of the other versions, 94.666667Mhz is just as clean as 106Mhz, 106.5Mhz, or 106.8000Mhz, 120.000Mhz, etc. It uses a much improved input circuit with a discrete differential pair limiter, accepting signals up to 200MHz of -13 to +7 dBm and producing a nice square wave compatible with the CPLD input characteristics. VCXO Freq. is Dividable from: 50 to 1023 (to 2047 in the version 02) by Binary selection of n0 through n9 (n10 in the version 02) (minimum Division = 50 and Maximum Division = 1023/2047).

Ref Freq.(10Mhz), is dividable by: 100, 80, 75, 60, 50, 40, 30 and 25, (or from 25 to 100 in 5 increments, in version 02).As on the classical version there are available both the leading edge type phase detector and the XOR gate

This design was developed in cooperation with Darrel VE1ALQ and a complete description of this version with a lot of detail can be found at: VE1ALQ site.

Locking to a 10MHz source (The original version).

The circuit is the classical implementation of a PLL with programmable dividers on both the reference and the signal, and uses a phase comparator specifically tailored to low phase noise. The article presented in DUBUS 3/2002 and here it is an English version, you can download "Locking VCXOs to 10MHz..."(35K)

Configuration files can be downloaded at the end of the page.

I can imagine many other configuration schemes for the local oscillators. Those interrested in using this circuit email me the table of frequencies desired and I will try to put together the needs of several users in two or three configuration files.

Universal VCXO Locking to a 10MHz source.

The circuit is now configured as a digital sampler PLL. This scheme has the ability to lock on multiples of a comparison frequency, resulting in very practical terms as a PLL that only locks the least significant digits of the locked VCXO.

The short article, waiting to be published, can be downloaded here "Universal Locking VCXOs to 10MHz."(15K)

The table with the lock points and corresponding configuration is inside the article.

This universal version fits in a smaller device so you can use original EPM3064ATC44 or the EPM3032ATC44.

Now I can't imagine other frequency configuration scheme for the usual VCXO - local oscillators.

Locking to a 1pps from a GPS receiver

The circuit implements a phase lag counter between the VCXO signal and the 1pps pulse edge. The phase lag value (14 to 16bit resolution) is converted to analog by a 1 bit DAC using and extremely fast PWM (pulse width modulation) scheme. The output, the VCXO control signal, is available in both positive and negative slope to cope with all VCXO tuning schemes.

This article is published in DUBUS 1/2003 and is here for you to download "Locking VCXOs to a GPS 1PPS output" (18.7K)

Feedback from builders.

Practical experiments shown that CPLDs speed grade "-7" as the EPM3032ATC44-7 and EPM3064ATC44-7 operate well up to 106.5MHz so useful for the 96MHz and below reflock applications. Darrel-VE1ALQ

Correction (12 Apr. 2003), the MAX Freq. for the EPM3064ATC44-7, and 303244-7 should be lowered to 93.6000, or 94Mhz. Of the 4 devices ATC44-7 only 2 will run consistently at 96Mhz... but all run fine at 93.600000Mhz. Darrel-VE1ALQ

Any comments:

Luis Cupido

Luis Cupido