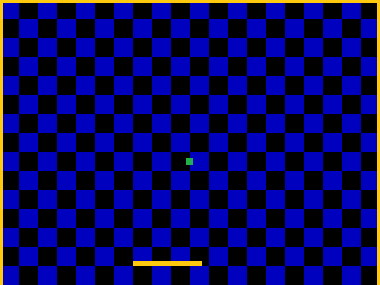

Na EP2C5 ploči nalazi se FPGA ALTERA Cyclone-II EP2C5T144C8, oscilator 50MHz, FLASH za konfiguraciju sistema, JTAG i SPI konektor za programiranje, taster za reset, 3x LED, stabilizatori napona 3.3V i 1.2V, napajanje čipa je 3.3V i 1.2V. Zahvaljujući programskim jezicima VHDL ili Verilog za projektovanje digitalnih sistema, omogućeno je programiranje video igara na ALTERA Cyclone II. Na ovu ploču dodati su, konektor za VGA monitor, kompozitni PAL ili RGB video izlaz, tasteri i rotacioni enkoderi za upravljanje igrom.

Izgled štampane ploče EP2C5, ALTERA Cyclone II:

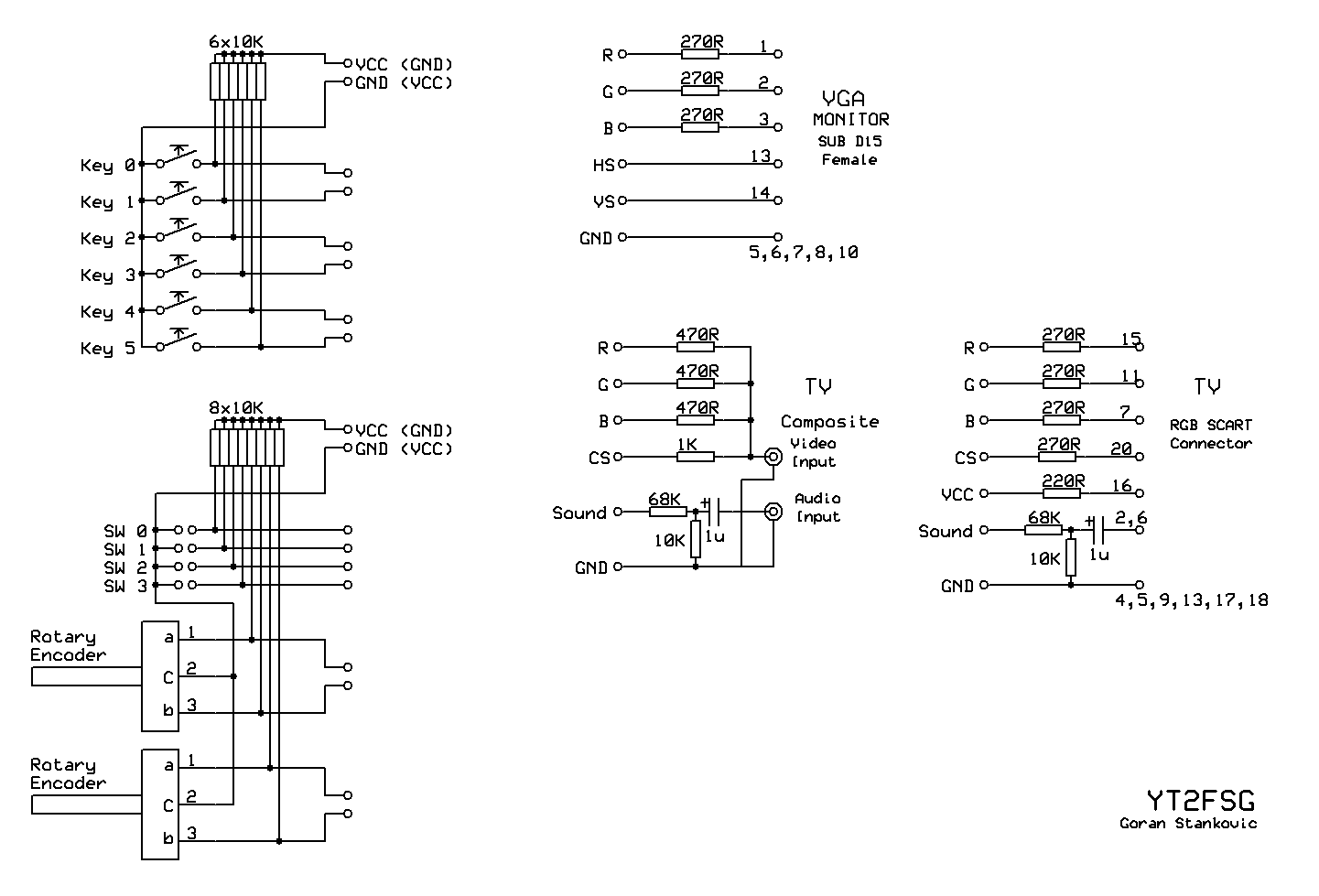

Kontrola igre Tennis:

SW0 – izbor video moda TV-RGB ili VGA

SW1 – u TV modu: izbor Sync na HSYNC ili na VSYNC; u VGA modu: scanline efekt

KEY0 – Reset igre

KEY2, KEY3 – kontrola levog igrača

KEY4, KEY5 – kontrola desnog igrača

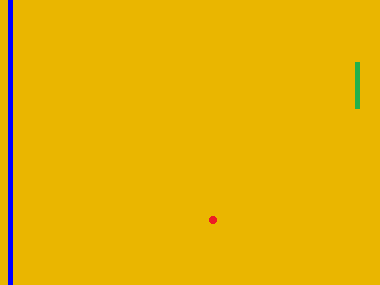

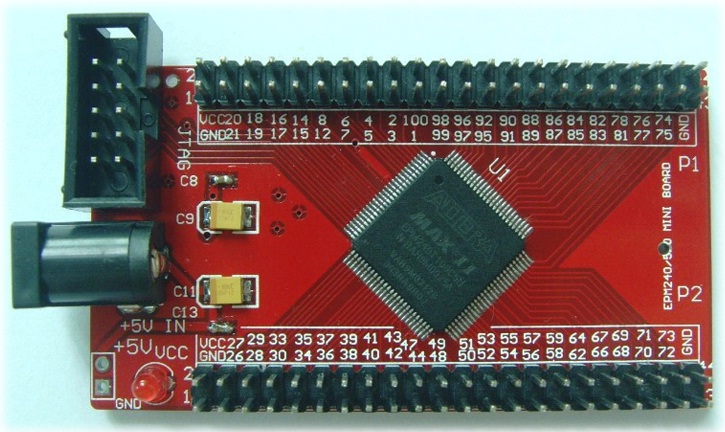

Na EPM240 ploči nalazi se CPLD ALTERA MAX-II EPM240T100C5, oscilator 50MHz, JTAG konektor za programiranje, stabilizator napona 3.3V, napajanje čipa je 3.3V. Zahvaljujući programskim jezicima VHDL ili Verilog za projektovanje digitalnih sistema, omogućeno je programiranje video igara na ALTERA MAX II. Na ovu ploču dodati su, konektor za VGA monitor, kompozitni PAL ili RGB video izlaz, taster za reset i tasteri i rotacioni enkoderi za upravljanje igrom.

Izgled štampane ploče EPM240, ALTERA MAX II:

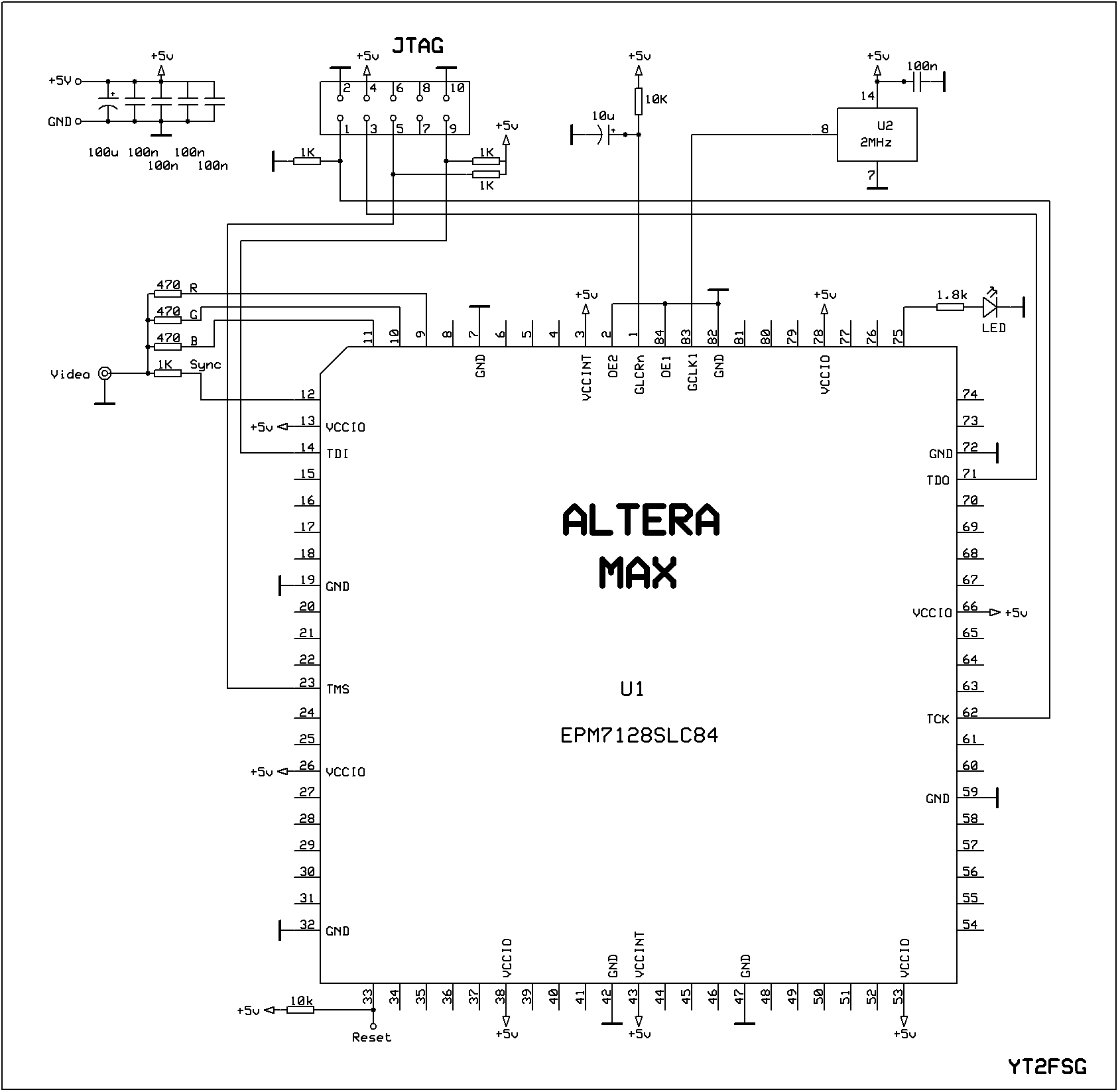

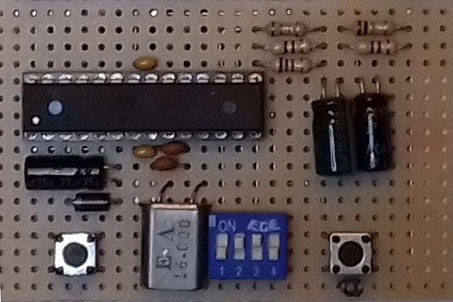

Na univerzalnu ploču zalemljen je CPLD ALTERA MAX EPM7128SLC84-15, podnožje sa oscilatorom 2MHz, LED i JTAG konektor za programiranje, napajanje čipa je 5V. Zahvaljujući programskim jezicima VHDL ili Verilog za projektovanje digitalnih sistema, omogućeno je programiranje video igara na ALTERA MAX. Na ovu ploču dodati su, konektor za kompozitni PAL ili RGB video izlaz, tasteri za reset i upravljanje igrom.

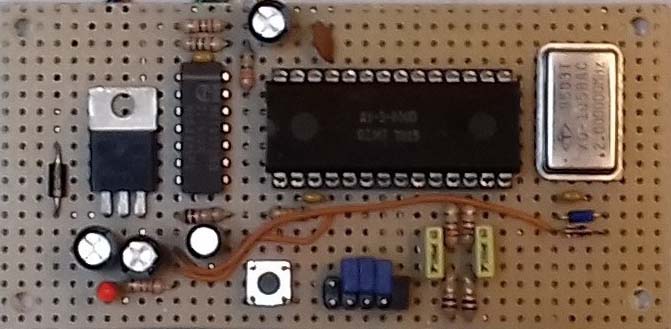

Izgled šeme i štampane ploče ALTERA MAX EPM7128, verzija YT2FSG :

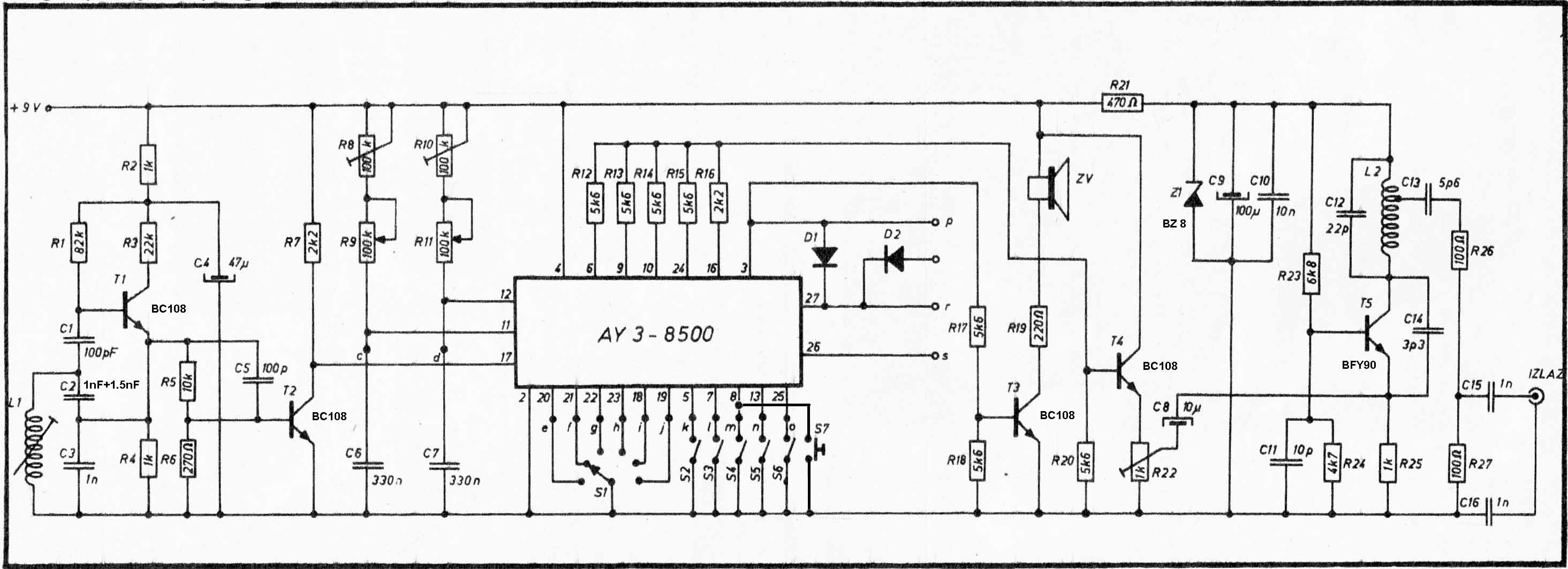

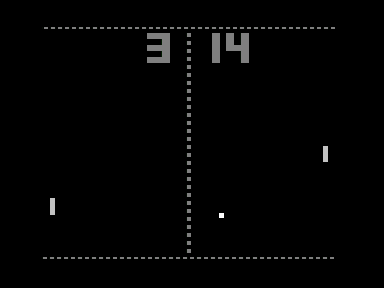

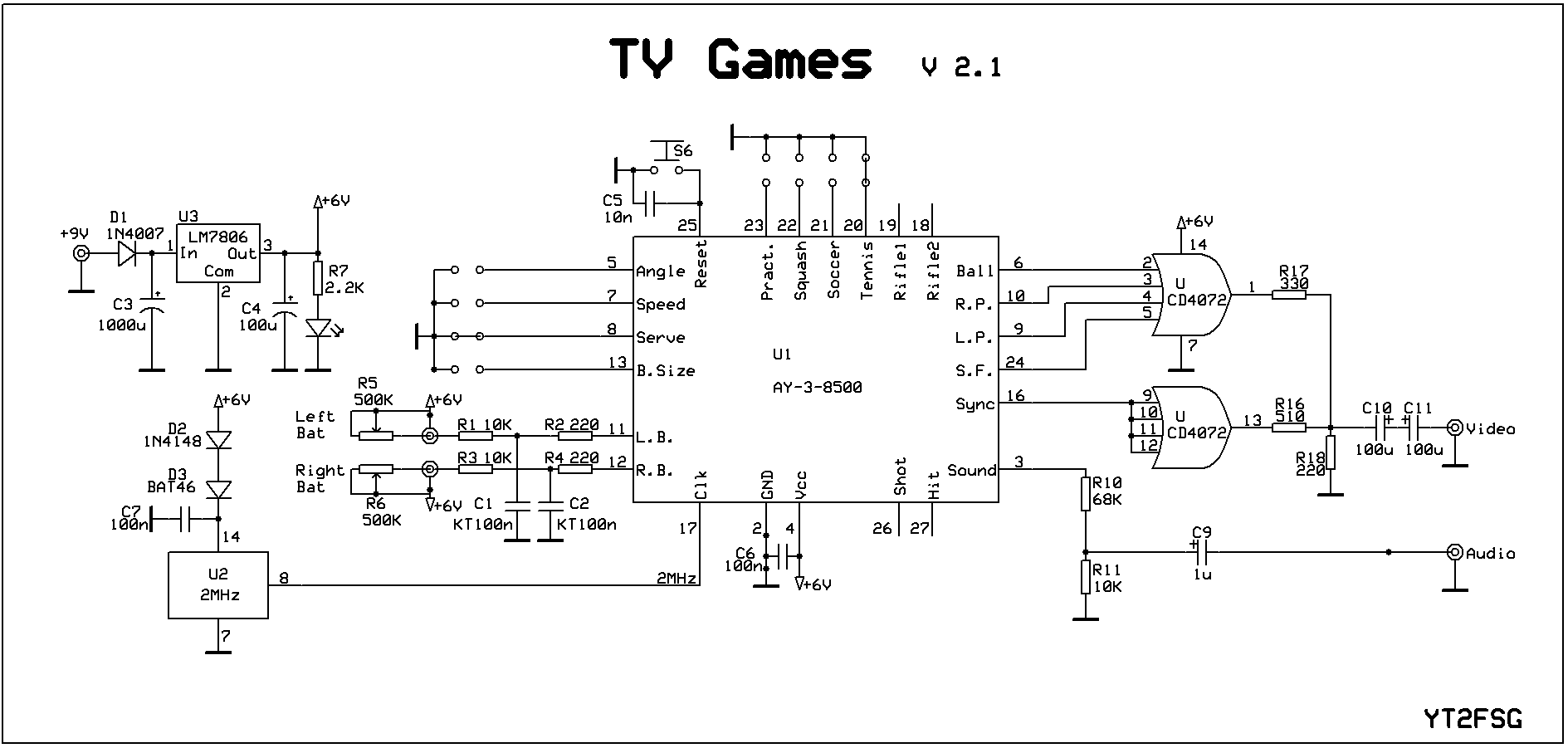

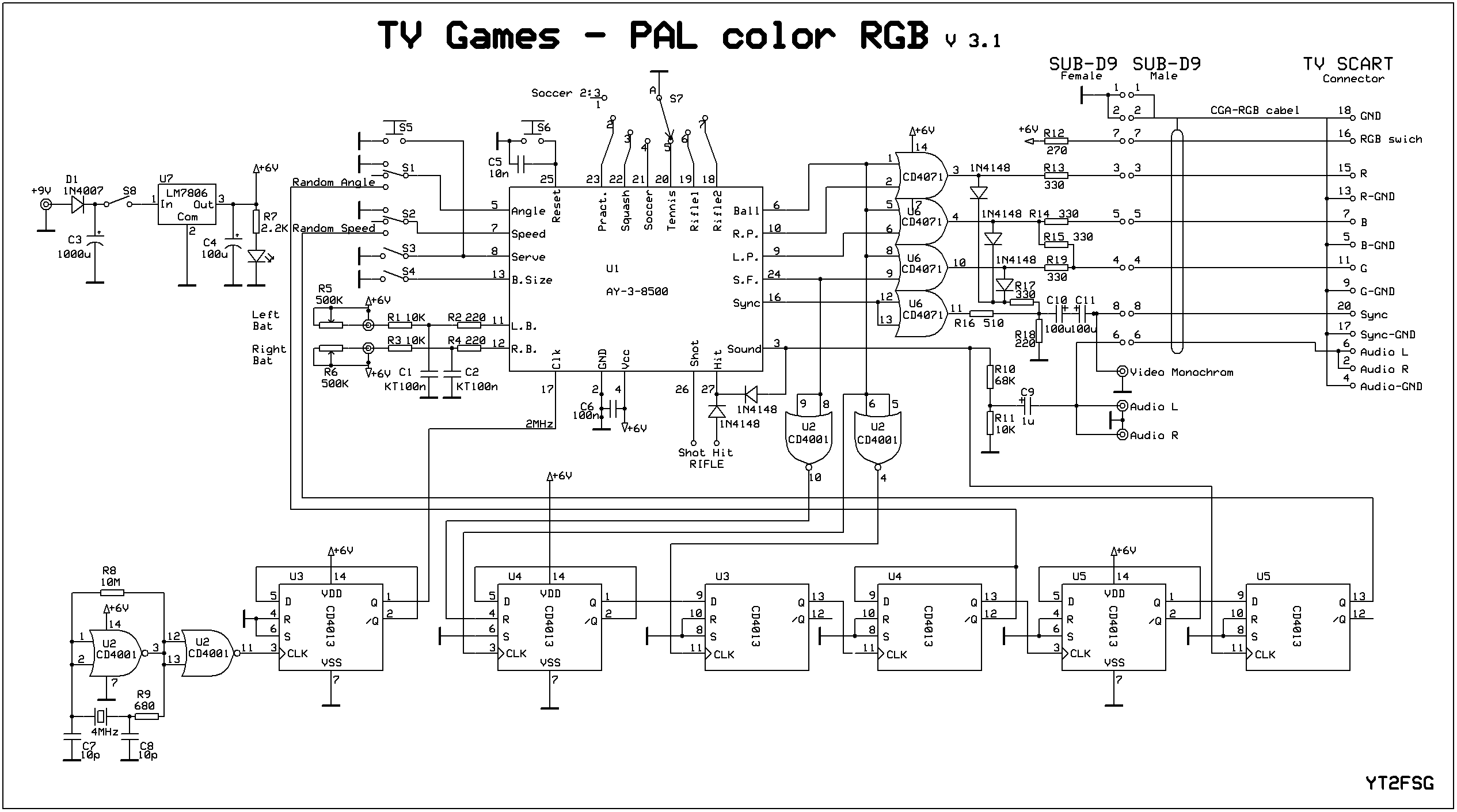

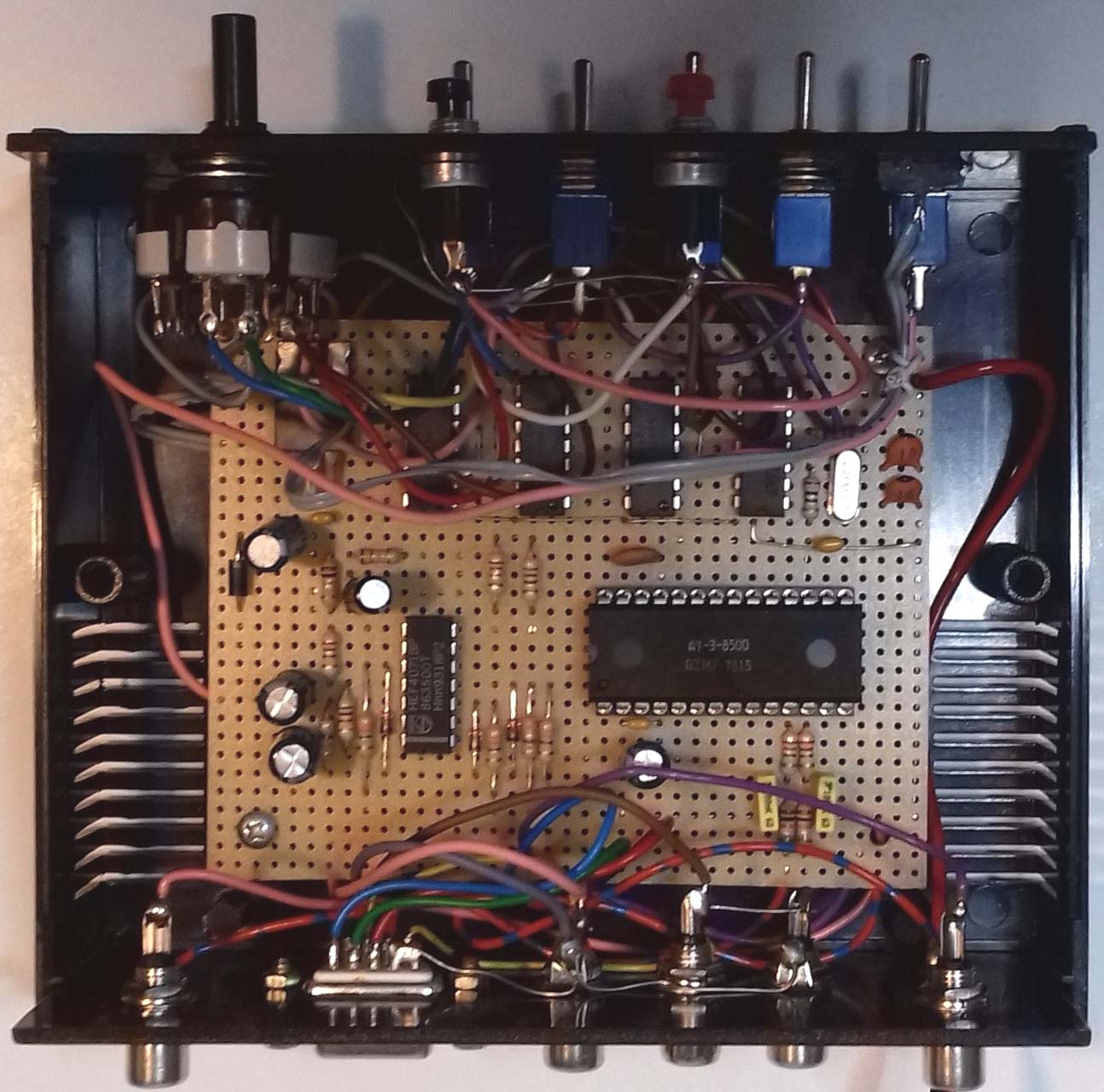

Ovi projekati zasnovan su na čipu AY-3-8500 kompanije General Instrument. Čip je izašao početkom 1976. godine ali prva dva kupca (Coleco i Magnavox) blokirala su proizvodnju neko vrijeme, jer su tada projekti zasnovani na TTL ili CMOS čipovima još uvek su bili u proizvodnji i prodaji.

U izradi ovih projekata korišćeno je upustvo za AY-3-8500 iz dokumenta GIMINI1978.pdf sa web sajta www.pong-story.com

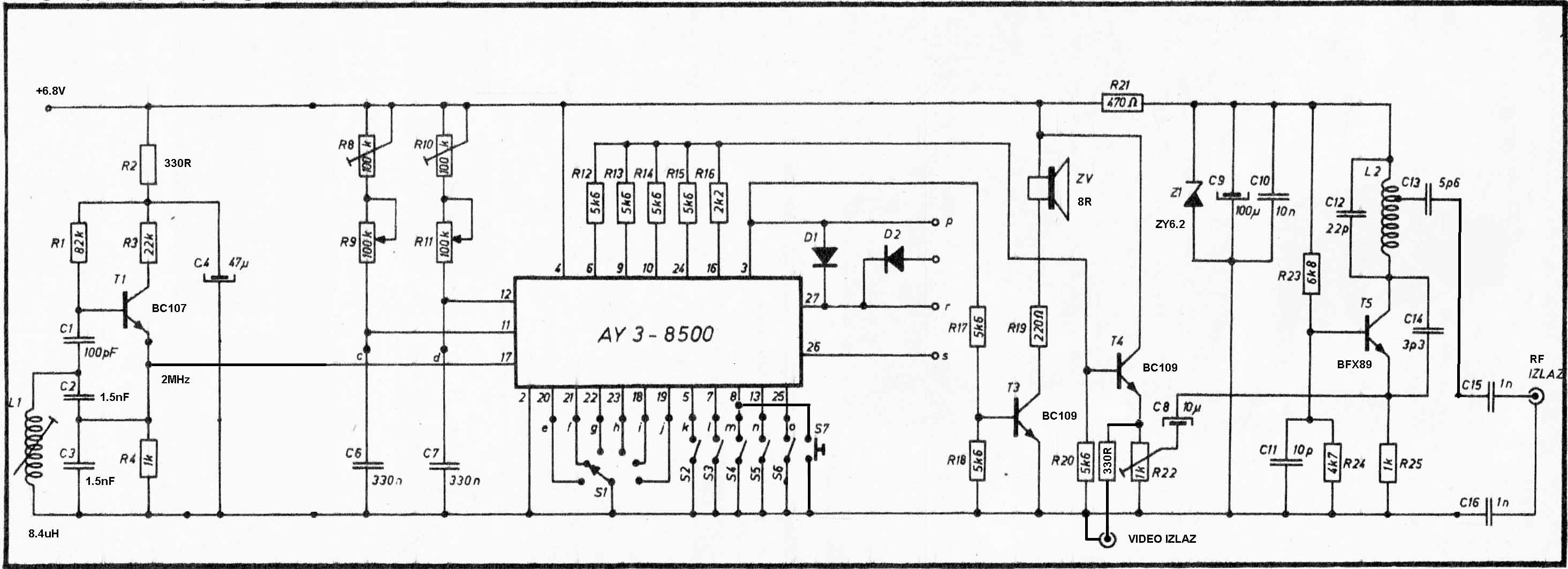

Izgled šeme i štampane ploče video igre AY-3-8500 sa minimum komponenti, verzija YT2FSG:

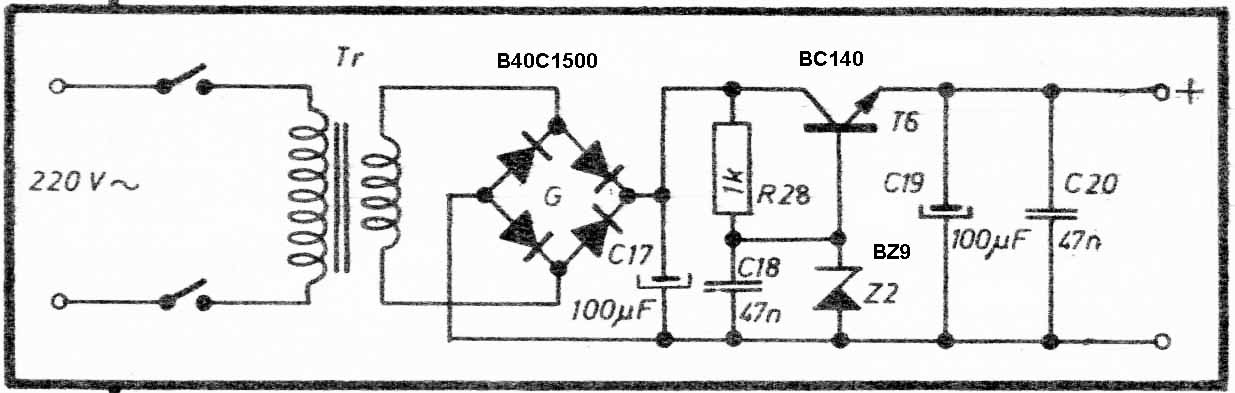

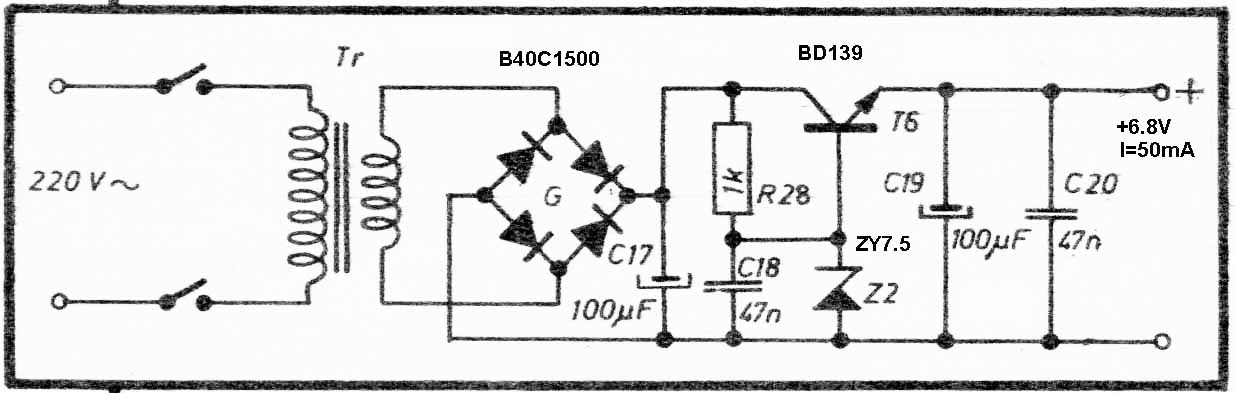

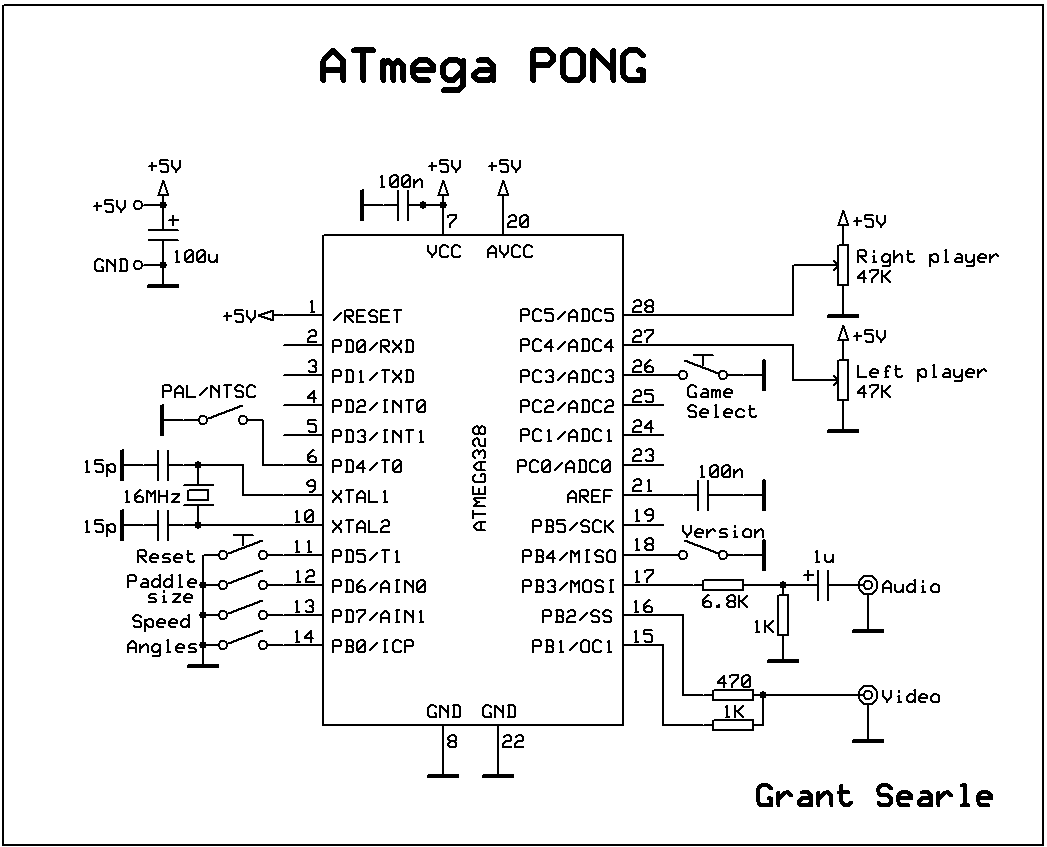

Ovaj klasični projekat TV igre objavljen je u časopisu SAM svoj majstor, Mart 1978. godine. Zasnovan na čipu AY-3-8500 kompanije General Instrument.

Skenirane stranice iz SAM-a, Mart 1978. godine: naslovna 1 2 3 4 5 6 7 8 9 10

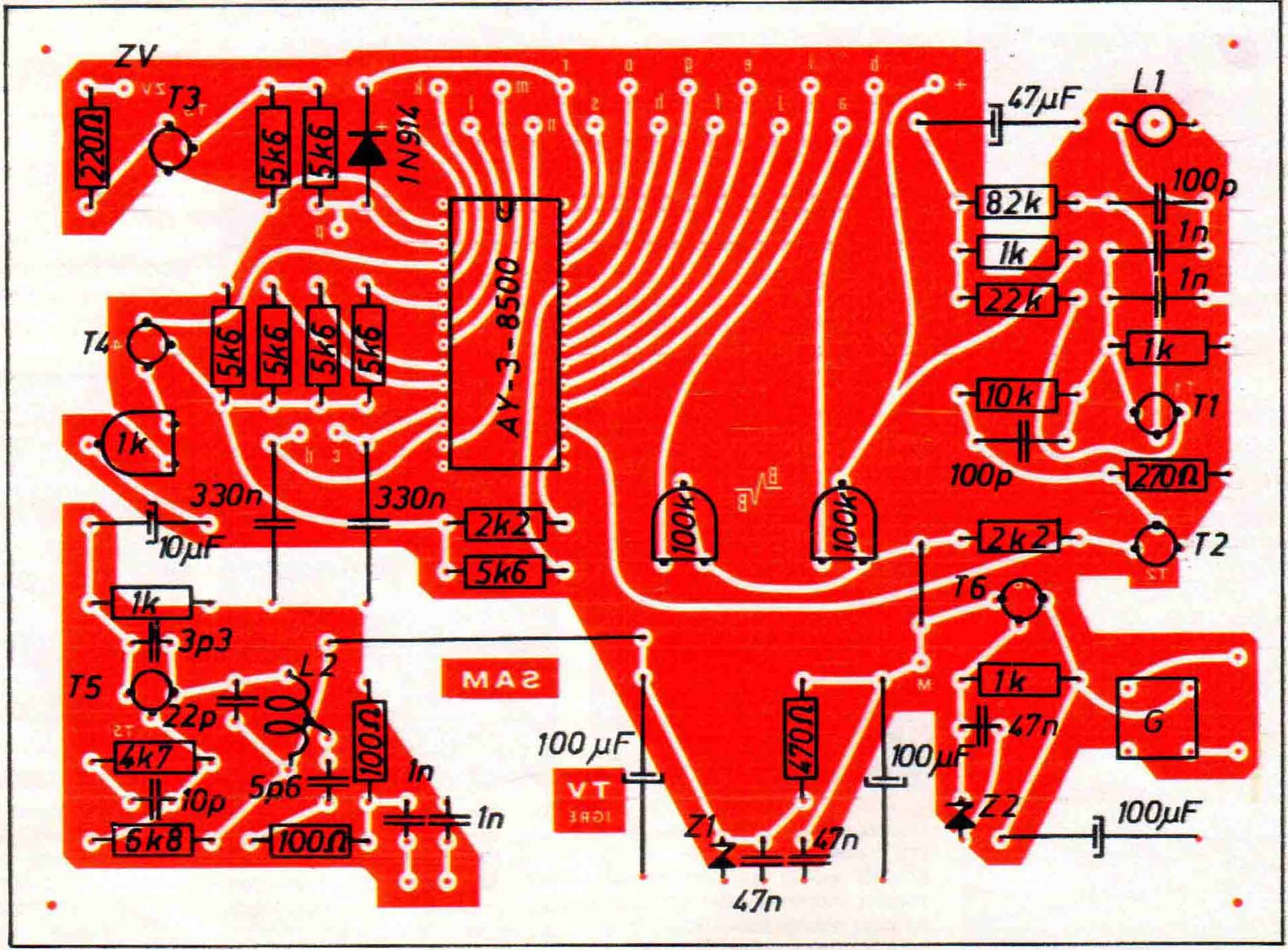

Izgled raspored komponenti na orginalnoj štampanoj ploči TV igre iz SAM-a: