## UHF AMPLIFIER DESIGN USING DATA SHEET DESIGN CURVES

### INTRODUCTION

The design of UHF amplifiers usually involves a particular set of device parameters of which  $h$ ,  $y$ , and  $s$  parameters are probably the most familiar. These parameters are commonly used to determine device loading (input and output) admittances for particular gain and stability criteria. The design procedure for determining gain and stability usually involves a mathematical solution, a graphical approach, or a combination of both.

This report describes a design technique for the unneutralized case whereby the device loading admittances are taken directly from device design curves. An example is given of how these design parameters are used to design a single stage 1 GHz microstrip amplifier and predicted results are compared to actual measured values. Practical circuit construction techniques are also discussed for the benefit of readers unfamiliar with microstrip techniques.

### STABILITY CONSIDERATIONS

Two very important methods<sup>1</sup> for expressing stability involve Linvill's stability factor "C" and Stern's stability factor "k". The first deals primarily with the device since an open termination is assumed on both the input and output and is formulated:

$$C = \frac{|y_{12} y_{21}|}{2g_{11} g_{22} - R_e (y_{12} y_{21})}.$$

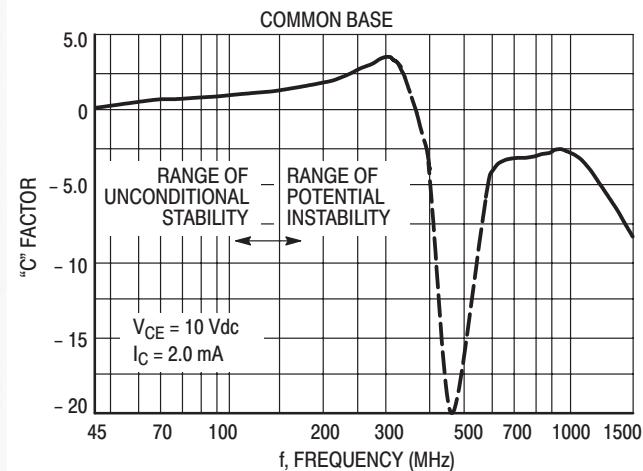

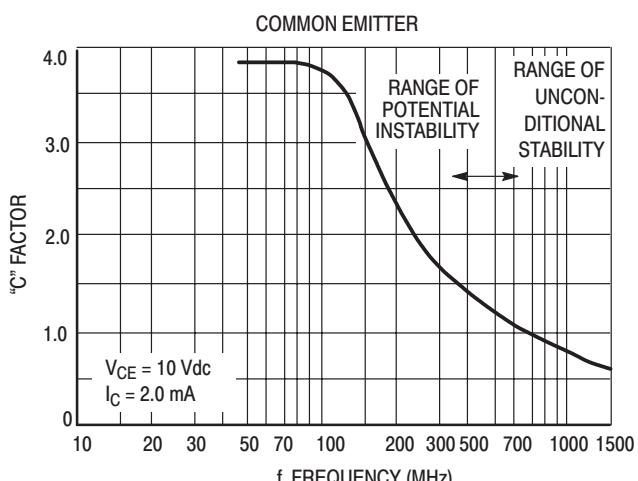

If "C" is greater than 1, the transistor is potentially unstable. However, if C is less than 1, the transistor is unconditionally stable. The C factor versus frequency for the common base and common emitter configurations (2N4957) are shown in Figures 10 and 17 respectively.

The second method is primarily circuit oriented and is used to compute the relative stability of an actual amplifier circuit for the particular source and load terminations used. If "k" is greater than 1, the circuit is stable. If "k" is less than 1 the circuit is potentially unstable.

Stern has developed equations for calculating the input and output loading admittances for maximum power gain with a particular stability factor,  $k$ . These values of input and output admittances in conjunction with the device parameters can then be used to calculate the transducer gain.<sup>1</sup>

$$k = \frac{2 (g_{11} + G_s) (g_{22} + G_L)}{|y_{12} y_{21}| + R_e (y_{12} y_{21})}$$

$$G_s = \sqrt{\frac{k [|y_{12} y_{21}| + R_e (y_{12} y_{21})]}{2}} \sqrt{\frac{g_{11}}{g_{22}}} - g_{11}$$

$$G_L = \sqrt{\frac{k [|y_{12} y_{21}| + R_e (y_{12} y_{21})]}{2}} \cdot \sqrt{\frac{g_{22}}{g_{11}}} - g_{22}$$

$$B_s = \frac{(G_s + g_{11}) Z_0}{\sqrt{k [|y_{12} y_{21}| + R_e (y_{12} y_{21})]}} - b_{11}$$

$$B_L = \frac{(G_L + g_{22}) Z_0}{\sqrt{k [|y_{12} y_{21}| + R_e (y_{12} y_{21})]}} - b_{22}$$

Where,

$$Z = \frac{(B_s + b_{11})(G_s + g_{22}) + (B_L + b_{22}) k (L+M)/2 (G_L + g_{11})}{\sqrt{k (L+M)}}$$

$$L = |y_{12} y_{21}|$$

$$M = R_e (y_{12} y_{21})$$

Defining D as the denominator in  $G_T$  expression yields:

$$D = \frac{Z^4}{4} + \frac{[k (L+M) + 2M] Z^2}{2} - 2NZ \sqrt{k (L+M)} + A^2 + N^2$$

where,

$$A = \frac{k (L+M)}{2} - M,$$

$$N = \text{Im} (y_{12} y_{21}),$$

and,

$Z_0$  = that real value of  $Z$  which results in the smallest minimum of D, found by setting,

$$\frac{dD}{dZ} = Z^3 + [k (L+M) + 2M] Z - 2N \sqrt{k (L+M)}.$$

equal to zero.

$$G_T = \frac{4 \text{Re} (Y_s) \text{Re} (Y_L) |y_{21}|^2}{| (y_{11} + Y_s) (y_{22} + Y_L) - y_{12} y_{21} |^2}$$

|           |                                           |

|-----------|-------------------------------------------|

| $k$       | = Stern's stability factor                |

| $G_s$     | = Real part of the source admittance      |

| $G_L$     | = Real part of the load admittance        |

| $B_s$     | = Imaginary part of the source admittance |

| $B_L$     | = Imaginary part of the load admittance   |

| $g_{11}$  | = Real part of $y_{11}$                   |

| $g_{22}$  | = Real part of $y_{22}$                   |

| $Y_L$     | = Complex load admittance                 |

| $Y_s$     | = Complex source admittance               |

| $G_T$     | = Transducer gain                         |

| $Y_{IN}$  | = Input admittance                        |

| $Y_{OUT}$ | = Output admittance                       |

| $G_{max}$ | = Maximum gain without feedback           |

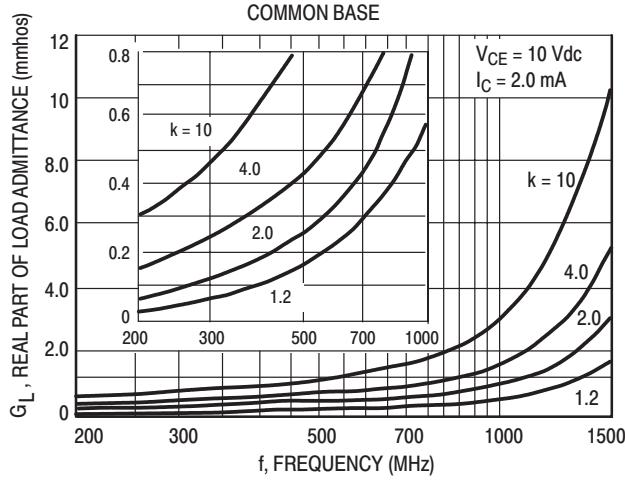

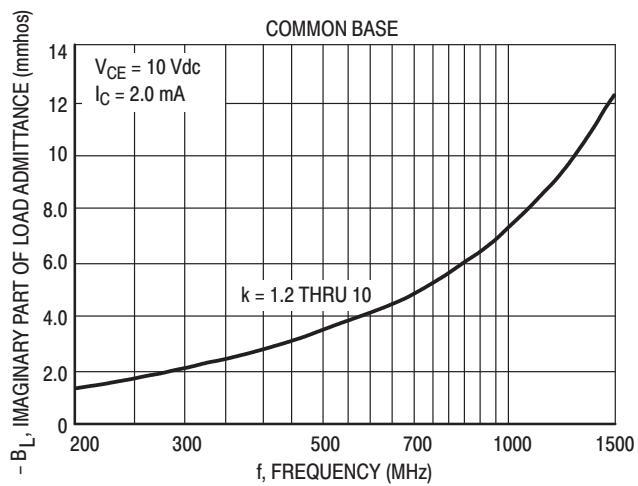

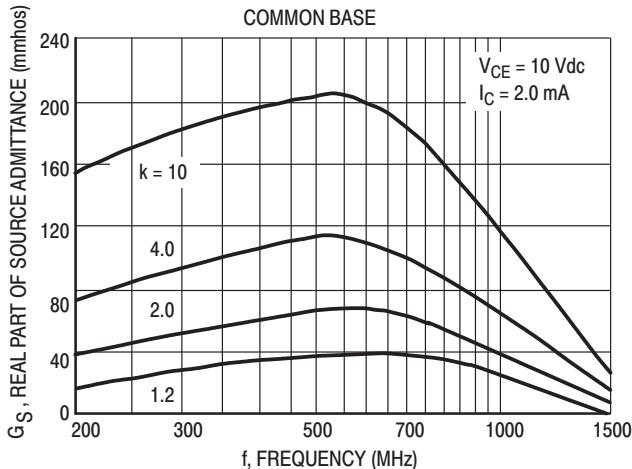

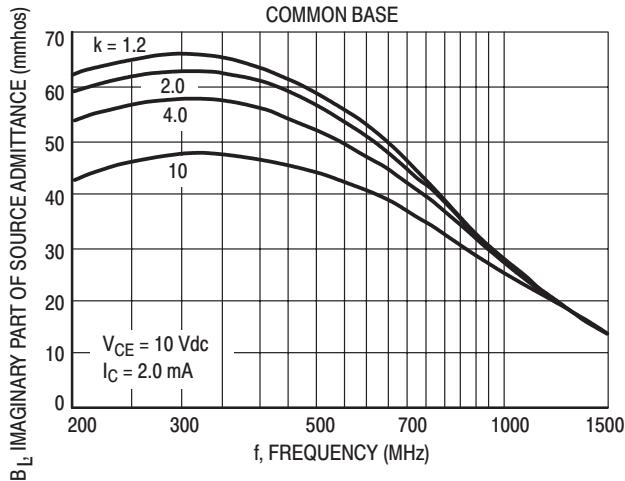

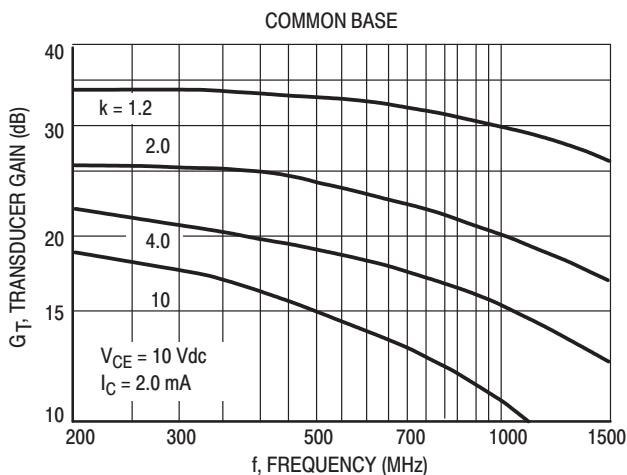

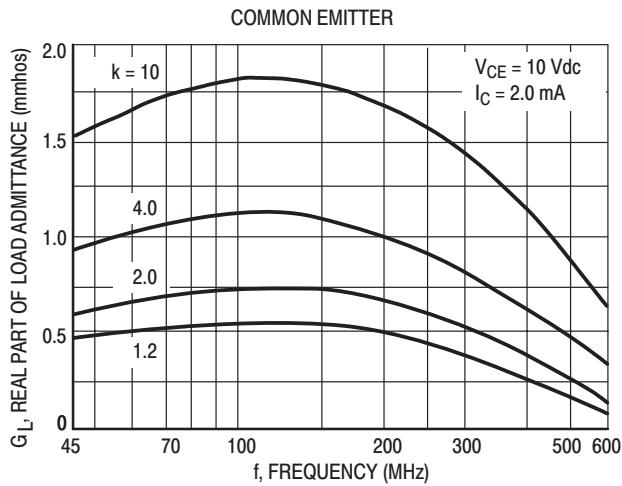

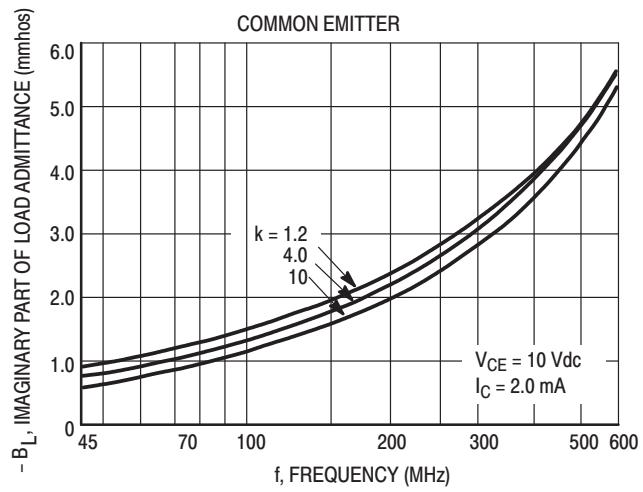

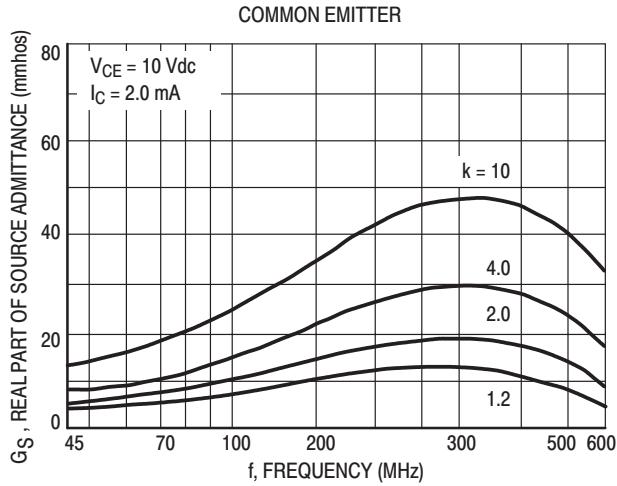

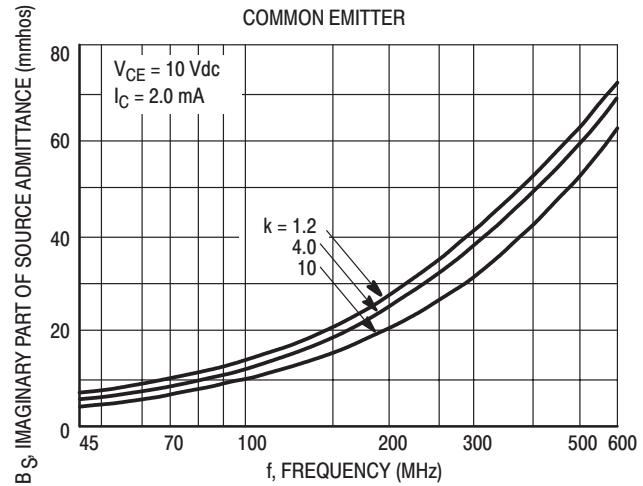

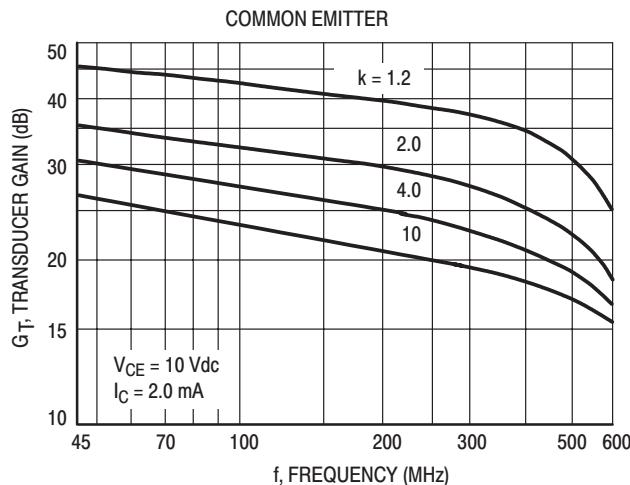

Computer solutions of these equations for various values of  $k$  versus frequency have been plotted in Appendix I for the 2N4957. These curves include common-base (Figures 10 through 16) and common-emitter (Figures 17 through 22).

From these curves, the designer can determine the input and output loading admittances for maximum power gain at a particular circuit stability. In addition, the transducer power gain under these conditions can also be determined. Thus the designer, rather than reading  $s$  or  $y$  parameters from a curve and using this information to design an amplifier, has all the design equations solved and presented in convenient, computer-derived design curves.

The following example demonstrates how these curves can be utilized in the design of a 1 GHz amplifier using the 2N4957. In addition, a second example is shown to demonstrate the special case where input admittance is determined primarily by noise figure considerations rather than by maximum power gain.

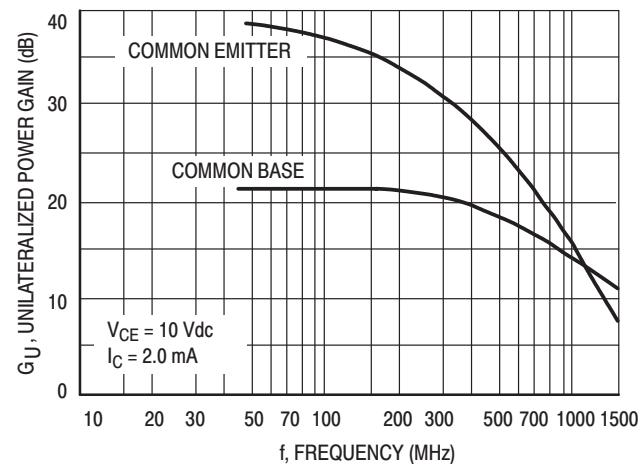

### 1 GHz AMPLIFIER DESIGN

A preliminary investigation of stability and power gain, common-emitter and common-base, can be quickly made from the design curves. For instance, the unilateralized gain (Figure 8) at 1 GHz is approximately 15 dB for either the common-emitter or common-base configuration. Also, the  $C$  factor for the common-base configuration (Figure 10) is greater than one and indicates potential device instability. However, the  $C$  factor for the common-emitter configuration (Figure 17) is less than one and indicates unconditional device stability.

Figures 16 and 22 are key curves that show transducer power gain for the common base and common emitter configuration respectively. Assuming a circuit stability factor of 4\*, power gain is approximately 15 dB, common-base. Although the common-emitter curve is not extended to 1 GHz (since this is a region of unconditional stability) power gain for  $k = 4$  would be obviously much less than 15 dB.

Using the common base configuration with  $k = 4$ , the required input and output admittance for maximum power gain can be determined directly from Figures 11 through 16.

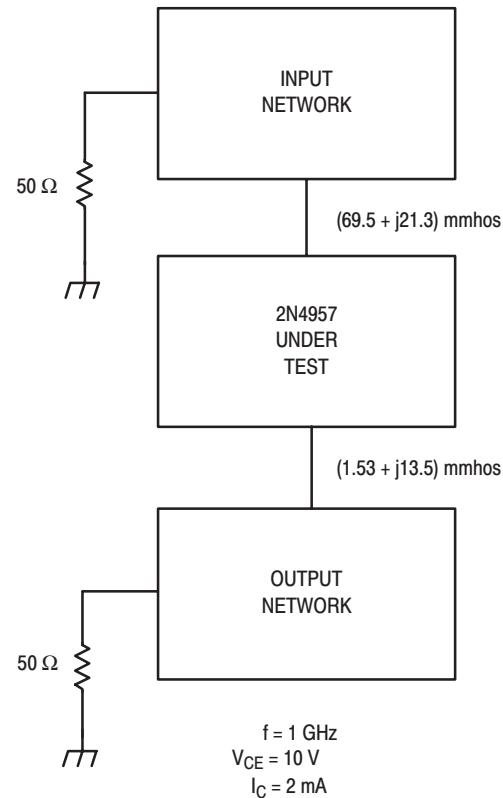

For instance, the real part of the output admittance can be read from either Figure 11 or 12. Figure 12 is an expanded version of Figure 11 and is intended to facilitate lower frequency use. The imaginary portion of the output admittance is shown in Figure 13. Figures 14 and 15 show the real and imaginary portions of the input admittance respectively. The resultant input and output admittances are shown in Figure 1 and are summarized:

Conditions: (2N4957)

$V_{CE} = 10$  V

$I_C = 2$  mA

$f = 1$  GHz

$G_T = 15$  dB

$k = 4$

Input admittance =  $69.5$  mmhos  $+j27.1$  mmhos

Output admittance =  $1.53$  mmhos  $-j7.46$  mmhos

It becomes apparent that the emitter must "see" an admittance of  $69.5$  mmhos shunted by a susceptance of  $+j27.1$  mmhos. The latter, in terms of a lumped constant element, would be a lossless capacitor. Likewise, the collector would be required to see an admittance of  $1.53$  mmhos shunted by  $-j7.46$  mmhos. The latter, in terms

of a lumped-constant element, would be a lossless coil. This loading will result in a stability factor,  $k$ , of 4 and a power gain of 15 dB, the maximum power gain possible for  $k = 4$ . This loading does not include stray capacitance. If stray capacitance is assumed to be 1 pF, the actual load is 1.53 mmhos,  $-j13.5$  mmhos (see Figure 1).

**Figure 1. Common Base Input and Output Admittances Including Stray Capacitance**

To facilitate instrumentation, both the source and load impedance will be 50 ohms. This admittance level must be transformed to the required device loading admittance. Micro strip techniques provide a convenient method of achieving this transformation without circuit reproducibility and component loss problems that are common with many lumped constant circuits at this frequency.

The Smith Chart is a convenient design tool for solving transmission line problems of this type. Since space does not permit, familiarity with this chart will be assumed.

Starting with the output circuit, both the 50 ohm (20 mmhos) load and the desired collector admittance are plotted on the Smith Chart (see Figure 2). As a starting point, a characteristic admittance of 20 mmhos will be assumed. First, the 20 mmho load is plotted (point A, Figure 2), then point B is plotted (1.53 mmhos  $-j13.5$  mmhos).

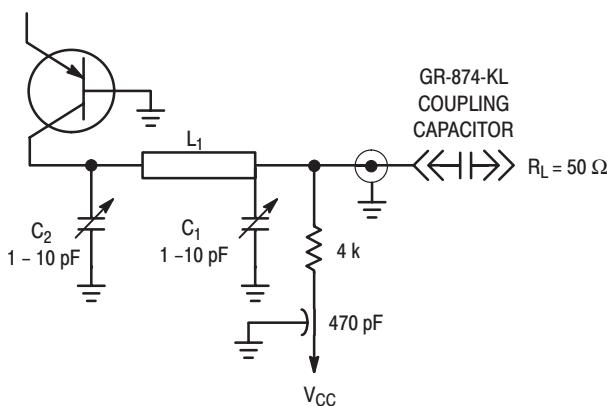

Although many different methods exist for transforming point A to point B (see Figure 2), a direct, and as it turns out, practical approach is that shown in Figure 3. This circuit uses  $C_1$  in parallel with  $R_L$  to vary the SWR of point A (Figure 2) to point C. Since point C has the same SWR as

\* For the purpose of this report a stability factor of 4 is chosen. Values of  $k$  less than 4 may not prove to be advantageous from the stand-point of regeneration and parameter spread.

**Chart Not Available Electronically**

Figure 2. Output Network Design

point B, a line  $L_1$  with an electrical length equal to  $0.405\lambda_2$  (point E) minus  $0.214\lambda$  (point D) will complete the transformation. Collector tuning is available with component  $C_2$ . This variable capacitor provides the difference between the assumed stray capacitance and the actual circuit stray capacitance.

The required SWR could have been realized by using an inductor in place of  $C_1$ . However, an inductor would have either forced the bias feed-point to be changed to the collector lead or necessitated a dc-isolated coil. Although this is readily attainable using transmission line techniques, the

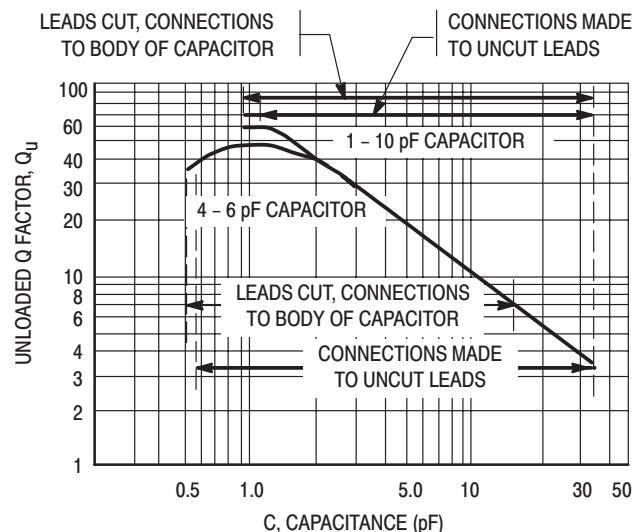

variable component  $C_1$  is more convenient. A typical curve of Q versus capacitance for  $(C_1)$  is shown in Figure 4.

The output bias is fed through a 4000 ohm resistor rather than an RF choke. The resultant 8 volt drop across this resistor is easier to contend with than the circuit instabilities sometimes associated with RF chokes.

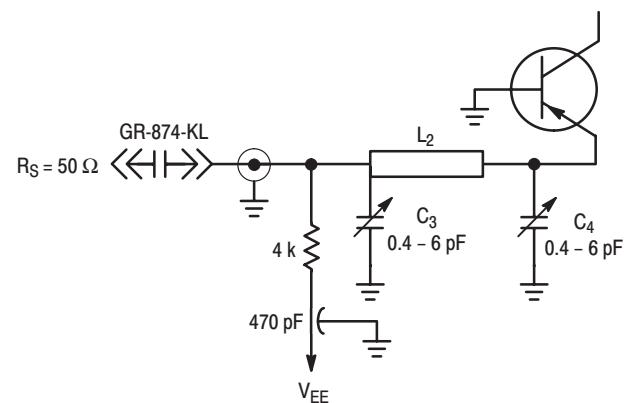

The same procedure is followed in designing the input network (see Figure 5). Again, a stray capacitance of 1 pF is assumed. Thus, the actual input loading becomes  $69.5 \text{ mmhos} + j21.3 \text{ mmhos}$ . First, the  $20 \text{ mmho}$  load is plotted (see Point T, Figure 6). Next, point W is plotted ( $69.5 \text{ mmhos} + j21.3 \text{ mmhos}$ ). Adjusting the SWR with  $C_3$  (point V) allows a transmission line of length  $L_2$  to transform the admittance at point V to the desired level at the base (point W).

Figure 4. Q versus Capacitance for  $C_1$  @ 1 GHz

Figure 5. Input Network

Chart Not Available Electronically

Figure 6. Input Network Design

## CIRCUIT CONSTRUCTION

The transmission line lengths  $L_1$  and  $L_2$  are readily transferred to micro-strip lengths once the wavelength and line-width are known. Hopefully, this information is available from the manufacturer, but if not, it must be measured before the design can be completed. The laminate used for this application required a line-width of approximately 0.16 inches for a 20 mmho characteristic admittance. This value proved adequate both from a realizable design solution on the Smith Chart and also from a practicable circuit construction standpoint.

The actual laminate thickness depends to a large extent on the desired characteristic impedance and the frequency of operation. The line thickness for a 50 ohm line is approximately 0.16 inch for a 1/16 inch laminate and approximately 0.035 inch for the same laminate 1/64 inch thick. As the intended frequency of operation is increased, the line width becomes a larger percentage of the line length.<sup>4</sup> Higher ratios of line width to length may result in undesirable modes of operation. Decreasing the laminate thickness results in a smaller line width for the same characteristic (assuming TEM operation) and a smaller line width to length ratio.

The dielectric constant for the material used was 2.6. The actual wavelength in the laminate is:

$$\lambda_{\text{actual}} = \frac{\lambda_{\text{air}}}{\sqrt{2.6}} = \frac{11.8 \text{ inches}}{\sqrt{2.6}} = 7.34 \text{ inches}$$

Since  $L_1 = 0.191\lambda$ ,

The physical length of  $L_1$  is 1.4 inches

Correspondingly,  $L_2$  is  $0.062\lambda$  or 0.455 inches.

It should be pointed out that the actual wavelength<sup>3</sup> for this laminate is somewhat larger than that calculated from the dielectric constant. A careful measurement<sup>4</sup> of wavelength versus characteristic impedance (line width) demonstrates this phenomena. The slight increase in wavelength (6%) from that calculated using the dielectric

constant was judged insignificant. However, this error increases for larger values of characteristic impedance and may prove to be quite significant for other laminates or narrower line widths. A good precaution would be to measure wavelength versus line width on each laminate used before TEM propagation is assumed.

Although the lines can be produced by a masking-etch process, adequate results can be obtained by cutting the desired strip from a thin copper sheet and gluing this strip to the teflon glass board. The latter is a convenient method for making rapid design changes.

The author observes several precautions which may or may not be necessary for all applications:

1. All breadboards have a ground strap which encompasses the outer periphery of the board. This strip is soldered to both the top and bottom copper sheets to effectively ground the outer periphery of the amplifier on all four sides. The circuit dimensions are held to a minimum to keep the ground planes as short as possible.

2. All RF connectors are carefully connected with grounding surfaces soldered to the ground plate. For instance, mount the connectors\* perpendicularly to the board at a point where the connection to the center conductor is a minimum length. Completely solder the outer conductor to the copper sheet on the opposite side of the board. Poorly mounted connectors may result in poor transitions and unpredictable impedance transformations. For example, tacking the outer barrel of this connector to the line side of the board may seriously alter the predicted impedance level at the collector.

The amplifier was constructed as specified and the admittance levels were measured at the emitter and collector pins. These admittance levels were checked and adjusted to the original design values with  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ .

The 2N4957 was then soldered directly into the circuit with minimum lead length. The resultant power gain was 14.3 dB and the noise figure, 6.5 dB, which is within 1 dB of the original design requirements. Attempts to re-adjust the input loading and output loading for lower noise figure resulted in lower noise figure with decreased circuit stability. Although the circuit (adjusted for minimum noise figure) didn't oscillate, the calculated  $k$  factor from the resultant input and output admittances was approximately 2.

## LOW NOISE DESIGN

Improvement in noise figure is possible by arbitrarily adjusting the input and output loading. For the purpose of this paper, the stability factor ( $k = 4$ ) will be retained.

However, the design curves represent the maximum power gain case. Although the circuit stability factor can be maintained at  $k = 4$ , varying the source loading will result in less power gain than indicated in the design curves.

The procedure for this case is as follows:

First, the optimum source resistance is calculated (see Appendix ) and found to be  $43\Omega$ .\*\* The calculated noise figure for this source is 5 dB. In addition, the source reactance was empirically determined to be inductive ( $j119\Omega$ ).

\*General Radio Cable Connector 874-G58B.

\*\*The actual value of optimum source resistance was empirically determined to be  $35\Omega$ . Consequently this value was used for the input circuit design rather than  $43\Omega$ .

Second, the collector loading was calculated for a stability factor of 4. Using these values of source resistance and stability factor, the calculated gain ( $G_T$ ) and collector loading is 11.8 dB and 3.41 mmhos – 7.5 mmhos (neglecting stray capacitance).

The output network was readily adjusted to the desired collector loading. However, the input line was too short and

required re-design (see Figure 7). The calculated value of this line length is 1.15 inches as contrasted with .46 inches used in the first example. The complete amplifier is shown in Figure 9.

The resultant power gain and noise figure was 11.8 dB and 5.5 dB. These figures compare well with the calculated design.

Chart Not Available Electronically

Figure 7. Low Noise Input Design

Figure 9. 1 GHz Amplifier

Figure 8. Unilateralized Power Gain versus Frequency

Figure 10. Linvill Stability Factor versus Frequency

**Figures 11 and 12. Load Admittance versus Frequency (Real)**

**Figure 13. Load Admittance versus Frequency (Imaginary)**

**Figure 14. Source Admittance versus frequency (Real)**

**Figure 15. Source Admittance versus Frequency (Imaginary)**

**Figure 16. Transducer Gain versus Frequency**

**Figure 17. Linvill Stability Factor versus Frequency**

Figure 18. Load Admittance versus Frequency (Real)

Figure 19. Load Admittance versus Frequency (Imaginary)

Figure 20. Source Admittance versus Frequency (Real)

Figure 21. Source Admittance versus Frequency (Imaginary)

Figure 22. Transducer Gain versus Frequency

## APPENDIX

## LOW NOISE DESIGN

The procedure followed in designing this amplifier is to first calculate the optimum source resistance for optimum noise figure and then calculate the collector loading for a required value of  $k$ .

A first approximation of optimum source resistance for optimum noise figure is:<sup>2</sup>

$$Rg_{F(opt)} = \sqrt{k_2^2 + \frac{k_1}{k_3}}$$

$$k_1 = rb + \frac{re}{2}$$

$$k_2 = rb + re$$

$$k_3 = \frac{1 + (B_o + 1) \left( \frac{f}{f_{\alpha b}} \right)^2}{2B_o re}$$

Assuming the above parameters for the 2N4957 are:

$$rb = 12.5 \text{ ohms}$$

$$re = 13 \text{ ohms}$$

$$B_o = 40$$

$$f_{\alpha b} = 1600 \text{ MHz,}$$

$$\therefore Rg_{F(opt)} = 43 \text{ ohms}$$

The noise figure using this source resistance is available from Nielsen's equation:<sup>2</sup>

$$NF = 1 + \frac{re}{2Rg} + \frac{rb}{Rg} + \frac{(Rg + re + rb)^2}{2B_o Rg re} \left[ 1 + (B_o + 1) \left( \frac{f}{f_{\alpha b}} \right)^2 \right]$$

Using the previous parameter values,

$$NF = 5 \text{ dB}$$

Since the impedance level is different at the base, the collector loading must be re-designed.

Using Stern's stability equator for  $k = 4$  (see Table 1):

$$k = \frac{2(g_{11} + G_s) - (g_{22} + G_L)}{|y_{12} y_{21}| + \text{Re}(y_{12} Y_{21})}$$

and calculating  $G_L$  for  $G_s = 25 \text{ mmhos}$  (40 ohms)

$$G_L = 3.41 \text{ mmhos}$$

The transducer gain can be calculated from these impedance levels:

$$G_T = \frac{4 \text{ Re}(Y_s) \text{ Re}(Y_L) |y_{21}|^2}{|(y_{11} + Y_s)(y_{22} + Y_L) - y_{12} y_{21}|^2}$$

$$G_T = 11.8 \text{ dB}$$

**Table 1.**

| $f = 1 \text{ GHz}$     | $V_{CB} = 10 \text{ V}$ | $I_C = 2 \text{ mA}$ |

|-------------------------|-------------------------|----------------------|

| $y_{ib} = 25 -j25$      |                         |                      |

| $y_{ob} = 0.55 +j7.54$  |                         |                      |

| $y_{fb} = -4.99 +j41$   |                         |                      |

| $y_{rb} = -0.01 -j1.19$ |                         |                      |

## REFERENCES

1. R. Hejhall, "RF Small Signal Design Using Admittance Parameters", Motorola Application Note AN-215A, Motorola Semiconductor Products, Inc., Phoenix, Arizona.

2. E. G. Nielsen, "Behavior of Noise Figure in Junction Transistors," Proc. IRE, Vol. 45, p. 957, July 1957.

3. F. Assadourian and E. Rimal, "Simplified Theory of Microstrip Transmission Systems", Proc. IRE, pp. 1651-1663, December 1953.

4. M. Ardit, "Experimental Determination of the Properties of Microstrip Components," Electrical Communication, December 1953.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and  are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

**MOTOROLA**

For More Information On This Product,

Go to: [www.freescale.com](http://www.freescale.com)

AN419/D