MONTE SEU

PLL SEM MISTÉRIOS

MONTE SEU

PLL SEM MISTÉRIOS MONTE SEU

PLL SEM MISTÉRIOS

MONTE SEU

PLL SEM MISTÉRIOS

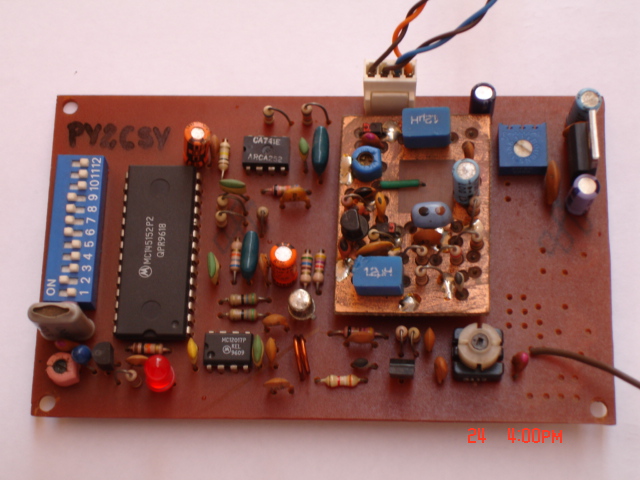

SINTETIZADOR COM PLL MC145152 E PRESCALER MC12017

Apresento aqui um excelente sintetizador com o PLL MC145162, Prescaler MC12017 e VCO utilizando o FET 2SK19. Pode ser utilizado para montagem de transmissores e receptores até 500MHz. A frequencia de operação é programada através de jumps. Podendo ser projetado programadores utilizando lógica CMOS ou TTL, microcontrolador ou microprocessador para programação de frequencia, inclusive com indicação digital da frequencia de operação.

DESCRIÇÃO DE FUNCIONAMENTO DO SINTETIZADOR

Na figura 1 é apresentado o diagrama esquemático do sintetizador que é formado por um circuito PLL simples. Um PLL é basicamente um servo-loop eletrônico. A função de um PLL é de detectar e seguir pequenas diferenças de fase e freqüência existente entre o cristal de referencia (pino 26 de CI1) e a freqüência de entrada (pino 1 IN). Tem por base CI1 que é um LSI (large scale integration). O oscilador de referencia de 10,240 MHz, ligado nos pinos 26 e 27 de CI1, é controlada pelo cristal de referencia XTAL1. O fruto da sintetização do PLL, já dividido por CI2 é aplicado no pino 1 de CI1. As duas freqüências, a do pino 1 e a do pino 26, são novamente divididas pelos divisores internos até ambas alcançarem o valor de 10KHz, quando tem suas fases comparadas pelo detector de fase, também interno. Este valor mútuo de 10KHz é a freqüência de referencia FR.O resultado dessa comparação de fase, a fase R e fase V, saem pelos pinos 7 e 8 de CI1 e são aplicadas nas portas, inversora (pino 2) e não inversora (pino 3), de CI3, que é um filtro passa-baixa, que tem a função de Filtro e Amplificador de Loop (amplificador de elo). CI1 então, segundo as informações das fases R e V, tem na sua saída, pino 6 uma tensão CC proporcional a diferença entre R e V, podendo ir de zero Volt a +9Vcc, sua tensão VDD. Esta tensão CC polariza o diodo varicap D2 (figura 2), determinando uma correção na capacidade do diodo e por extensão uma correção na freqüência do VCO, formado pelo FET 2SK19. Conforme a tensão do pino 6 de CI3, podemos corrigir a freqüência do VCO, segundo a frequencia programada, evitando que a mesma varie e mantendo-se precisa tal como a frequencia do cristal XTAL1. Isto em termos absolutos (% de precisão) e em termos de variação de temperatura +-5PPM. O sinal de áudio modulador, aplicado no terminal de entrada, atua na tensão de D1, promovendo somas algébricas instantâneas na tensão CC do mesmo e com isso, mudando instantaneamente a capacidade de D1,ocasionando variações instantâneas da frequencia do VCO, o que na realidade, é um real desvio de frequencia, que neste caso, em radiodifusão FM, é de no máximo +-75KHz. D2, C4, CT1 e L1 formam o circuito tanque do oscilador controlado a voltagem.

O sinal do VCO, é entregue a Q2, que é um isolador (Buffer), que isola o VCO das influências dos circuitos seguintes. O sinal retirado no coletor de Q2 é enviado para o divisor (Prescaler) CI2, que direciona o sinal para retorno ao LSI, formando o elo de fase amarrada (PLL - Fhase Locked loop). CI2 é um divisor digital do tipo ECL (emitting coupled lógic) cujos níveis lógicos "0" e "1" estão a +3,15 e +4,05 Volts respectivamente. Não tendo que gastar tempo para saturar ou cortar a corrente de trabalho, este divisor é capaz de operar com freqüências até 500MHz. A divisão normal é de 64 vezes. Mas como temos necessidade de divisões fracionárias, uma parte do Duty Cicle (ciclo útil) é transformado em divisor por 65 vezes, pelo SWALLOW PULSE (pulso inibidor SP) e o integrado deixa de contar o 65º pulso, tantas vezes quantas necessárias. Isto é feito pelo pino 9 de CI1 que manda o Swallow Pulse ao pino 1 de CI2. O pino 9 retira esta informação da "lógica interna de controle", cuja função, ter ou não ter o Swallow Pulse, depende da frequencia que se queira sintetizar, informação esta dada pela programação dos jumps conectados a CI1. A frequencia do VCO, então, é dividida por 64 ou 65 por CI2 (divisor P), é aplicada ao pino 1 de CI1, onde sofre nova divisão, agora pelo divisor interno Contador N de 10 Bits, programado pelos jumps através dos pinos N0 até N9, chamado divisor mais significativo. Conforme a escolha da frequencia programada nos jumps, aplicando nos seus pinos 10 Bits, como por exemplo: 0110011101. A saída deste divisor já é aplicada no detector de fase interno e está pronta para ser comparada. Mas o sinal do pino 1, também é dividido pelo divisor Contador A de 6 Bits, também programado pelos jumps através dos pinos de A0 até A5, chamado divisor menos significativo, ou do Swallow Pulse. Colocando-se todas as entrada N's e A's em nível "0" (Zero), sintetiza-se a menor frequencia possível, e vice versa, com nível 1, a maior frequencia possível dentro do sistema incluso no LSI. Com N9 (pino 20) aterrado, são sintetizadas freqüências dentro do VHF; com N9 em "1", sintetiza-se freqüências acima de 250MHz. Portanto N9 sempre estará aterrado para as freqüências da faixa de 88 a 108 MHz. Quando qualquer pino de programação ficar aberto, estará com nível lógico "1" devido resistores (Pullup Resistor) internos ao LSI. Então, com o pré-divisor CI2 e com os divisores internos do LSI (CI1), descemos a frequencia sintetizada pelo VCO em VHF para 10KHz, necessário à comparação de fase feita pelo detector interno do LSI. Portanto, qualquer que seja a frequencia sintetizada pelo VCO, isto nos obriga a baixa-la sempre para 10KHz, divisão esta obtida inicialmente, por CI2 comandado pelo Swallow Pulse e principalmente pelos divisores internos N e A, programadas pelos jumps através dos 13 bits.

Com o retorno do sinal ao detector de fase, completamos o loop (ELO), pois os sinais R e V "nascem" no detector, produtos da comparação que são do sinal do VCO, pino 1, com o sinal do oscilador de referencia do cristal XTAL1, nos pinos 26 e 27. Note que ambos sinais devem ser divididos até 10KHz, que é o real valor da frequencia de referencia FR.

A amarração do elo (locking loop) é essencial à sintetização precisa e controlada de qualquer frequencia. Se o loop perder o lock (Lock Less), um sinal de alarme será gerado pelo detector de fase, excitando o detector de amarração (Lock Detect) e colocando no pino 28 um trem de pulsos digitais da ordem de 9KHz, que saturam Q1, fazendo acender o led D1, indicando com isso, ou que que a frequencia programada está fora do ajuste do VCO ou que há falha no loop.

A freqüência de oscilação do cristal XTAL1, desenvolvida nos pinos 26 e 27 de CI1, é aplicada no divisor Contador R de 12 Bits e após, aplicada ao detector de fase, já na frequencia de 10KHz. Este divisor é alimentado com 12 bits, programado pelos pinos 4 (RA0), 5 (RA1) e 6 (RA2), que através desses pinos programam uma memória ROM (memória somente de leitura) interna ao próprio LSI. Esta memória é alimentada por um decodificador binário de três linhas de entrada e oito de saída, cujas três entradas são os pinos 4, 5 e 6. Então, para programar a divisão da frequencia já conhecida de um cristal, basta aplicar ou não, níveis terra nos pinos RA0, RA1 e RA2. Aplicando um "jump" para terra, garante-se nível "0" (zero) na entrada aterrada. Deixando-a livre, sem nada, o Pullup Resistor interno ao LSI, transmite nível "1" automaticamente à entrada e a mesma lê "1" obviamente. Como temos três entradas isto nos dá 8 possibilidades de programar o divisor e poderíamos ter até outras 7 freqüências para ser dividida. Logo abaixo teremos a explicação de como calcular a frequencia de referencia.

No VCO e através de C17, é retirado o sinal de RF para aplicação em circuitos externos como receptores e transmissores. Atenção! Deverá ser montado um isolador (Buffer), que isolará o VCO das influências dos circuitos seguintes.

CI3 pode ser substituído pelo LM741.

Para os mais habilidosos, L1 pode ser impressa na própria placa de circuito impresso.

FIGURA 1- PLL - Para copiar a figura, clicar com o botão direito do mouse sobre a figura e selecione "salvar figura como", ou para ver, simplesmente clicar sobre a figura.

FIGURA 2- VCO

CÁLCULOS E PROGRAMAÇÃO DOS DIVISORES

Iniciaremos pelo divisor da frequencia de referencia.

* Observe na tabela abaixo que o nível lógico "0" o pino está aterrado, e nível lógico "1", o pino está aberto.

|

PINO 6 RA2 |

PINO 5 RA1 |

PINO 4 RA0 |

VALOR DA DIVISÃO |

| 0 | 0 | 0 | 8 |

| 0 | 0 | 1 | 64 |

| 0 | 1 | 0 | 128 |

| 0 | 1 | 1 | 256 |

| 1 | 0 | 0 | 512 |

| 1 | 0 | 1 | 1024 |

| 1 | 1 | 0 | 1160 |

| 1 | 1 | 1 | 2048 |

* 01) - Vamos calcular a frequencia do cristal mais adequado ou propício.

Ex.: Multiplicando 1024 da tabela por 10.000Hz (frequencia de referencia) = 10.240.000 ou 10,240MHz => Este é o valor do cristal usado no nosso projeto, devido ser mais comum no mercado. Programar os jumps conforme tabela acima.

FR = Freq. Cristal de Referencia ÷ 1024 = 10KHz

FR = Frequencia de Referencia

FC = Frequencia do Cristal de Referencia

FC = FR x 1024 => 10.000 x 1024 = 10.240.000KHz = 10,240MHz

FC = 10,240MHz

* 02) - Agora vamos calcular os valores dos divisores "N" e "A" do PLL (CI1).

FS = Freqüência de Saída

N = Divisor Programável

A = Divisor Programável

FR = Freqüência de Referência

P = Divisor 64 - PRESCALER

DT (Divisão Total) = (Divisor P x Divisor N) + Divisor A

Na prática se resume em duas divisões aritméticas. Por exemplo, para a freqüência de saída do VCO igual a 100,1 MHz, a primeira divisão é feita como segue:

DT = FS (em Hz) ÷ FR (em Hz)

DT = 100100000 ÷ 10000 = 10010

10010 é a divisão total da conjugação dos 3 divisores P,N e A. A segunda divisão é mais simples e é feita como segue:

DT = (DIVISOR P x DIVISOR N) + DIVISOR A

Como P é fixo em 64, e DT já foi calculado, para se achar o valor de N dividimos assim:

DIVISOR N = DT ÷ DIVISOR P => N = 10010 ÷ 64 = 156,....

O resultado é um valor inteiro, 156 no exemplo, com uma parte fracionária que não interessa e deve ser desprezada.

O divisor A é o resto da divisão 10010 por 64, que é 26. Isto porque 156 x 64 = 9984, logo 10010(DT) – 9984 = 26.

Logo DT = (P x N) + A => DT = (64 x 156) + 26 = 10010

O exemplo acima ficou da seguinte forma:

FS = Freqüência de Saída = 100,100 MHz

N = Divisor Programável = 156

A = Divisor Programável = 26

FR = Freqüência de Referência = 10 KHz

P = Divisor 64 - PRESCALER

Ver detalhes em blocos do PLL em Aprenda Como Funciona o PLL

* 03) - Com os valores dos divisores "N" e "A", vamos ver como programar os jumps.

Os valores encontrados de N = 156 e A = 26, são decimais, logo teremos que converte-los em binário como segue:

Tabela com a conversão do valor 156.

| DIVISÕES SUCESSIVAS

VALORES EM DECIMAL |

RESTOS

VALORES EM BINÁRIO |

156

0 78 |

0 = N0 |

78

0 39 |

0 = N1 |

39

1 19 |

1 = N2 |

19

1 9 |

1 = N3 |

9

1 4 |

1 = N4 |

4

0 2 |

0 = N5 |

2

0 1 |

0 = N6 |

1

1 0 |

1 = N7 |

| --- | * N8 = 0 |

| --- | * N9 = 0 |

Na tabela temos os valores de N0 a N9. Lembrando que nível lógico "0", o pino do CI deverá ser aterrado, e nível lógico "1", o pino deverá ser deixado aberto.

* N8 e N9 não tiveram resto, mas mesmo assim deverão ser aterrados.

Tabela com a conversão do valor 26

| DIVISÕES SUCESSIVAS

VALORES EM DECIMAL |

RESTOS

VALORES EM BINÁRIO |

26

0 13 |

0 = A0 |

13

1 6 |

1 = A1 |

6

0 3 |

0 = A2 |

|

3 1 1 |

1 = A3 |

1

1 0 |

1 = A4 |

|

--- |

* A5 = 0 |

Na tabela temos os valores de A0 a A5. Lembrando que nível lógico "0", o pino do CI deverá ser aterrado, e nível lógico "1", o pino deverá ser deixado aberto.

* A5 não teve resto, mas mesmo assim deverá ser aterrado.

Todas informações necessárias para o projeto do PLL foram dadas, porém qualquer dúvida contate-me pelo e-mail py2csy(arroba)yahoo.com.br arroba => @

Inicio da contagem de acessos a este artigo em 17/08/2013

![]()