## **ChipCorder Application Information**

| Application Information Section                                | ISD1000A Series | ISD1100 Series | ISD1200 Series | ISD1400 Series | ISD1500 Series | ISD2500 Series | ISD33000 Series | ISD4002 Series | ISD4003 Series |

|----------------------------------------------------------------|-----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|

| Application Information Introduction                           | •               | •              | •              |                | •              | •              | •               |                |                |

| For All ISD Products                                           |                 |                |                |                |                |                |                 |                |                |

| Microphone and Speaker<br>Selection                            |                 |                |                |                |                |                |                 |                |                |

| Address Segmentation<br>Resolution                             |                 |                |                |                |                |                |                 |                |                |

| Frequently Asked Questions                                     |                 |                |                |                |                |                |                 |                |                |

| Stand Alone/Parallel Interface                                 | Products        | <b>)</b>       |                |                |                |                |                 |                |                |

| Device Operation                                               |                 |                |                |                |                |                |                 |                |                |

| Using the Device                                               |                 |                |                |                |                |                |                 |                |                |

| Basic Addressing                                               |                 |                |                |                |                |                |                 |                |                |

| Operational Modes                                              |                 |                |                |                |                |                |                 |                |                |

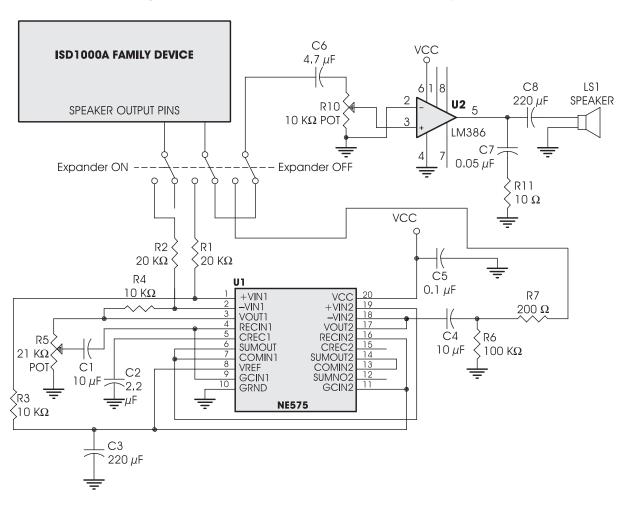

| Circuit Examples for ISD1000A and ISD2500 Products             | •               |                |                |                |                | •              |                 |                |                |

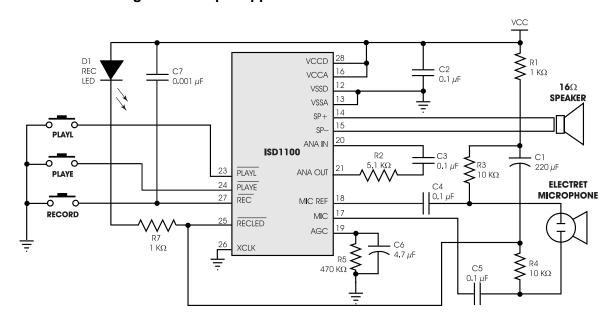

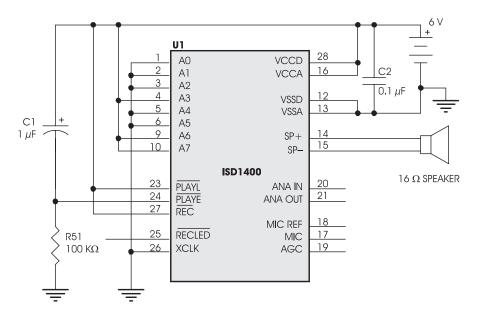

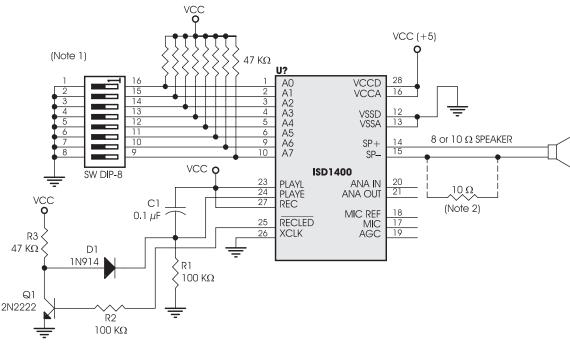

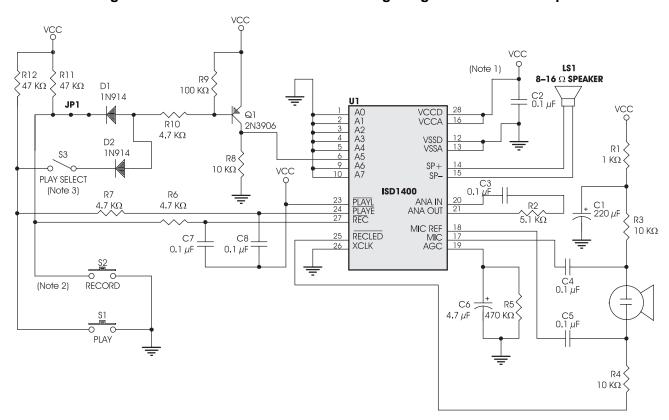

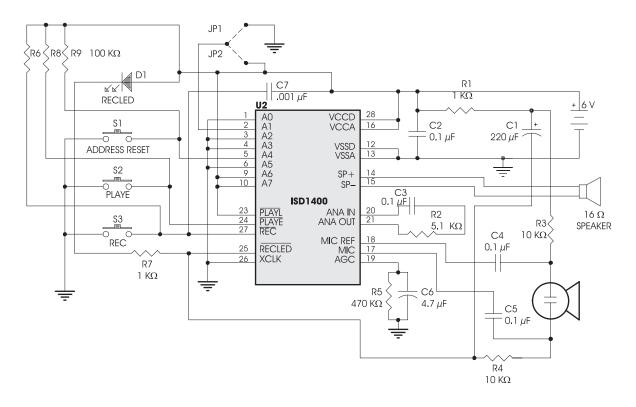

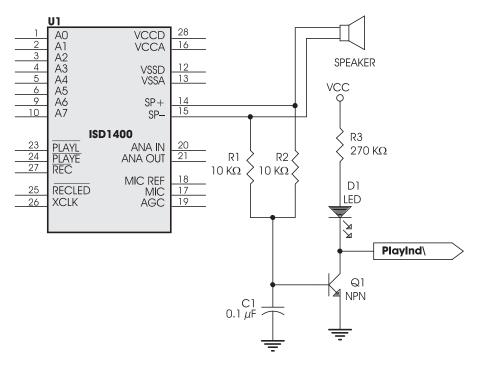

| Circuit Examples for ISD1100,<br>ISD1200, and ISD1400 Products |                 |                |                |                |                |                |                 |                |                |

| Good Audio Design Practices                                    |                 |                |                |                |                |                |                 |                |                |

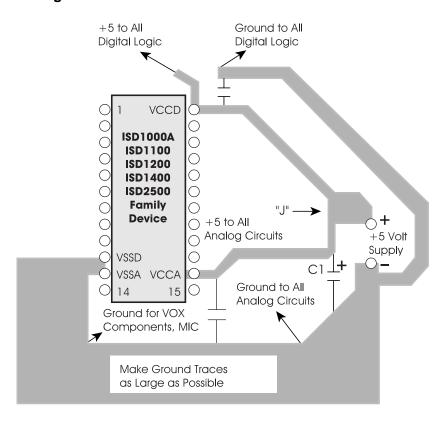

| Single-Chip Board Layout<br>Diagrams                           |                 |                |                |                |                |                |                 |                |                |

| Application Information Section                                          | ISD1000A Series | ISD1100 Series | ISD1200 Series | ISD1400 Series | ISD1500 Series | ISD2500 Series | ISD33000 Series | ISD4002 Series | ISD4003 Series |

|--------------------------------------------------------------------------|-----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|

| Serial Interface Products                                                |                 |                |                |                |                |                |                 |                |                |

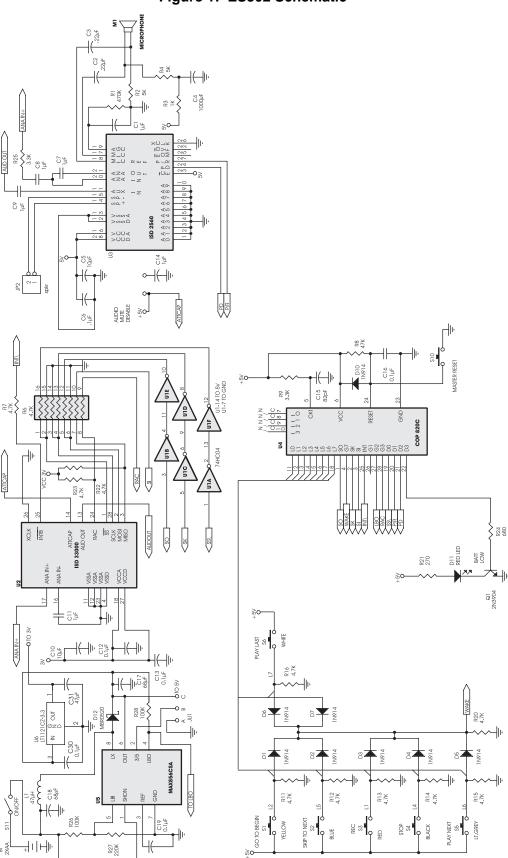

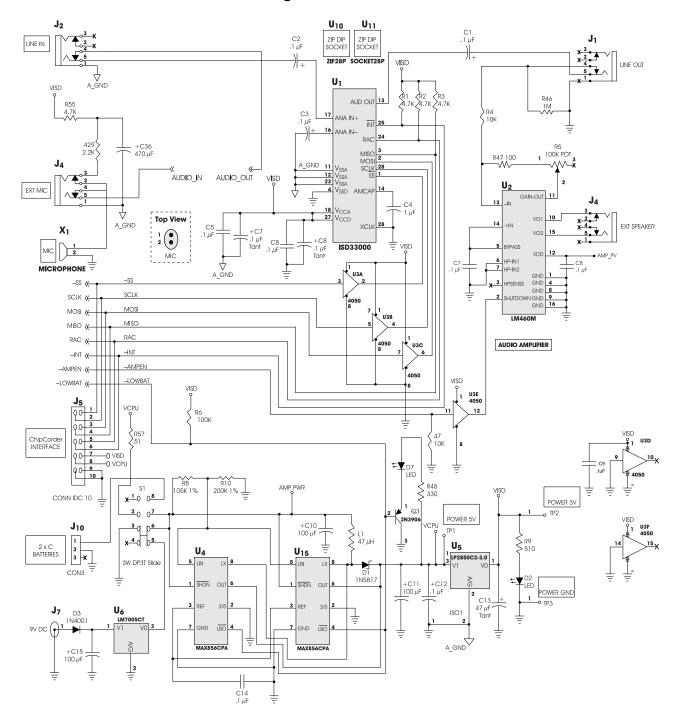

| Introduction and Circuit<br>Examples                                     |                 |                |                |                |                |                | •               | •              | •              |

| Example Circuit: Minimum I/O<br>Application                              |                 |                |                |                |                |                |                 | •              |                |

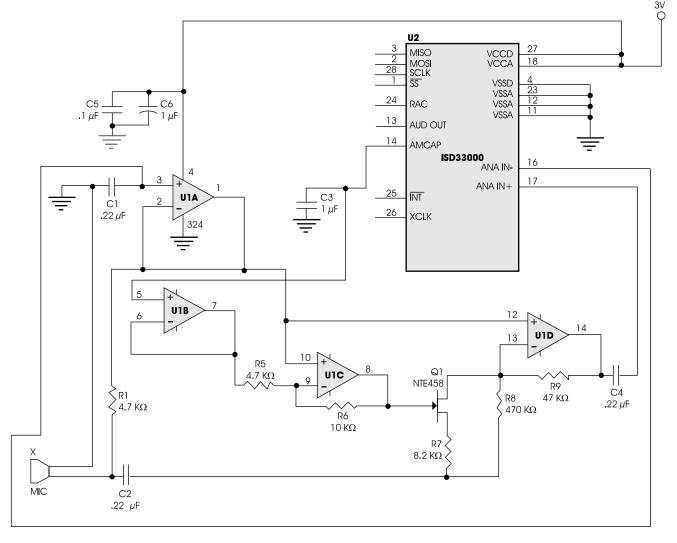

| Example Circuit: Microphone<br>Circuit                                   |                 |                |                |                |                |                |                 | •              |                |

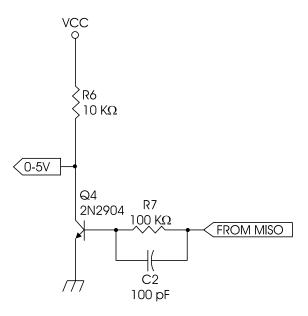

| Example Circuit: Single<br>Transistor 3-Volt Speaker Driver              |                 |                |                |                |                |                |                 |                |                |

| Using the ISD33000 Series with 5-Volt Powered Processors                 |                 |                |                |                |                |                |                 |                |                |

| Operations, Tricks, and<br>Techniques in the ISD33000<br>Series          |                 |                |                |                |                |                |                 |                |                |

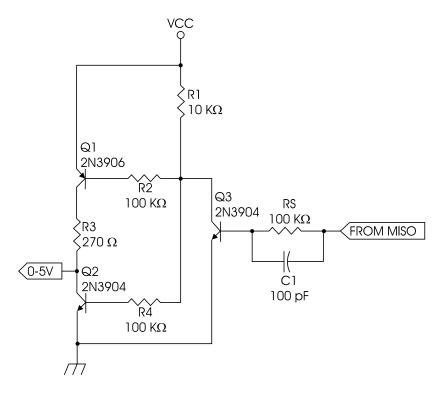

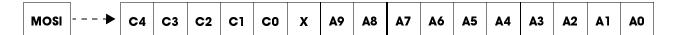

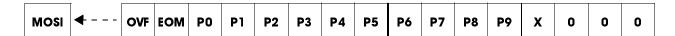

| Using the ISD33000 Device with a Microcontroller                         |                 |                |                |                |                |                |                 |                |                |

| Using the ISD33000 Device with a Low-Cost Motorola Microcontroller       |                 |                |                |                |                |                |                 |                |                |

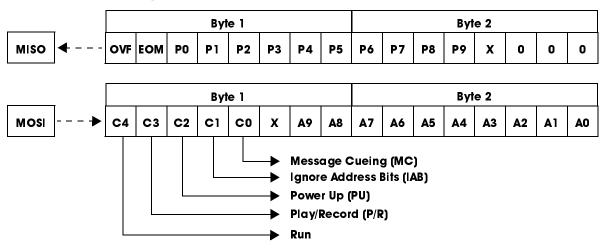

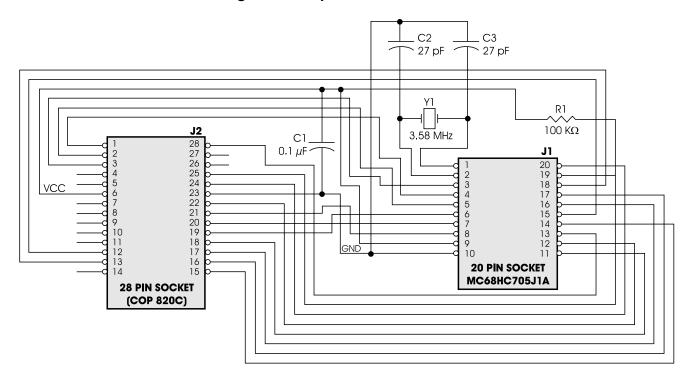

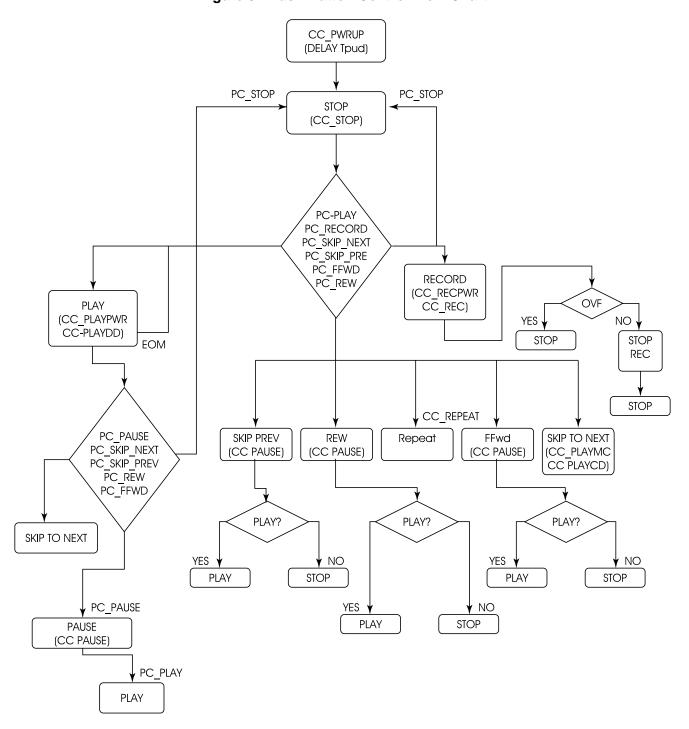

| Message Management in the ISD33000 Series                                |                 |                |                |                |                |                |                 |                |                |

| A "C" Language Source Code<br>Example to Use with the<br>ISD33000 Series |                 |                |                |                |                |                |                 |                |                |

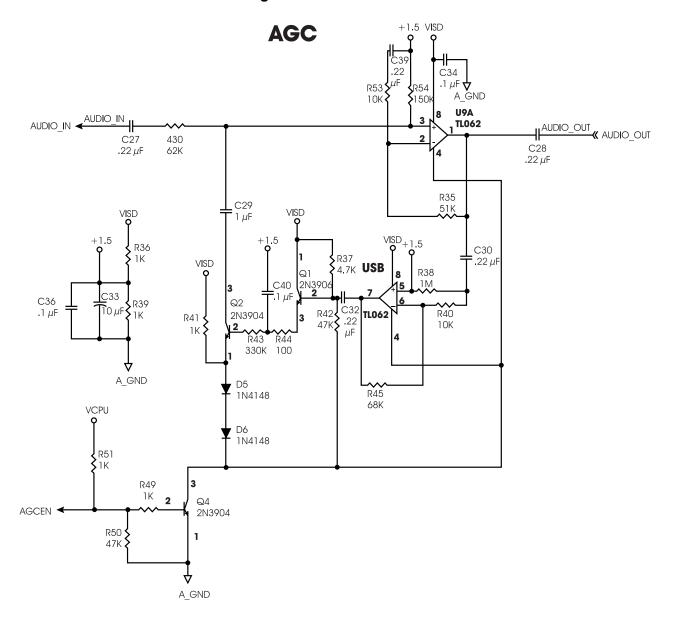

| AGC Circuit for the ISD33000<br>Series                                   |                 |                |                |                |                |                |                 |                |                |

2 Voice Solutions in Silicon<sup>™</sup>

### APPLICATION INFORMATION FOR ALL ChipCorder PRODUCTS

### Introduction

#### THE TECHNOLOGY AND THE PRODUCTS

The ISD patented ChipCorder technology brings analog data into the semiconductor memory world. This "break through" EEPROM storage method allows analog data to be written directly into a single cell without A/D or D/A conversion. This results in:

- Increased density over equivalent digital methods

- Nonvolatile storage of analog data

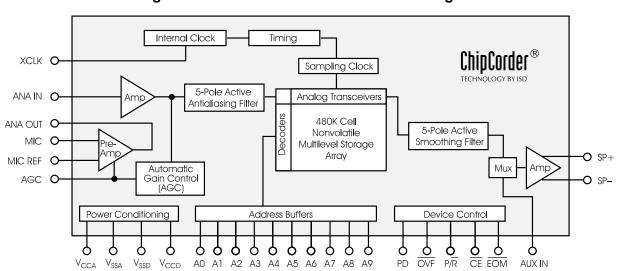

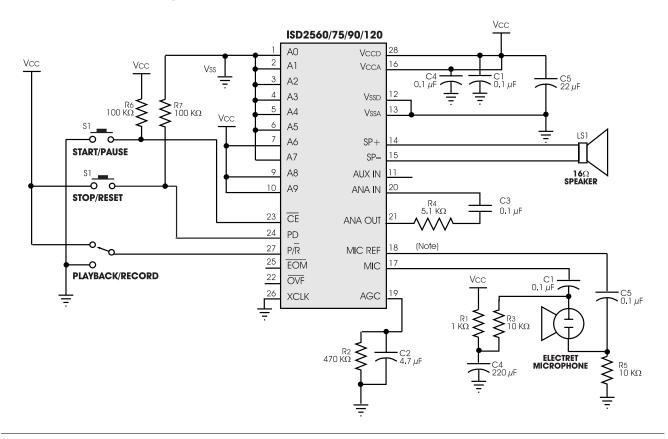

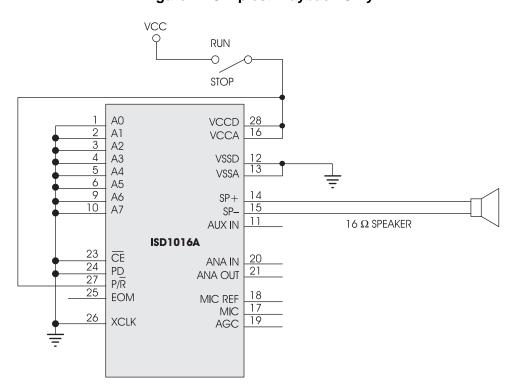

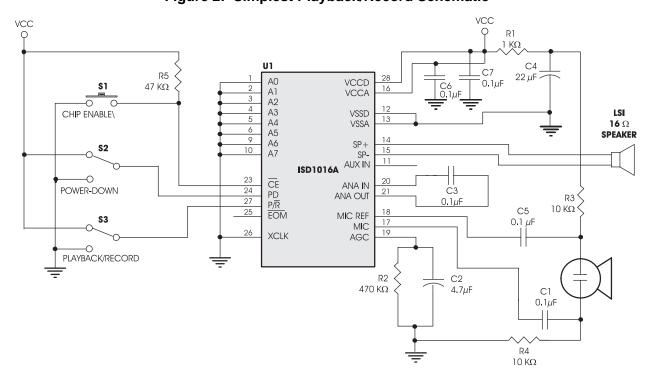

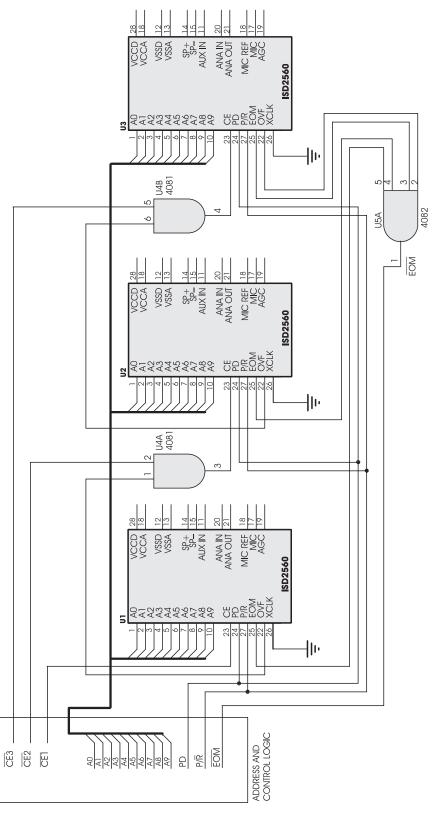

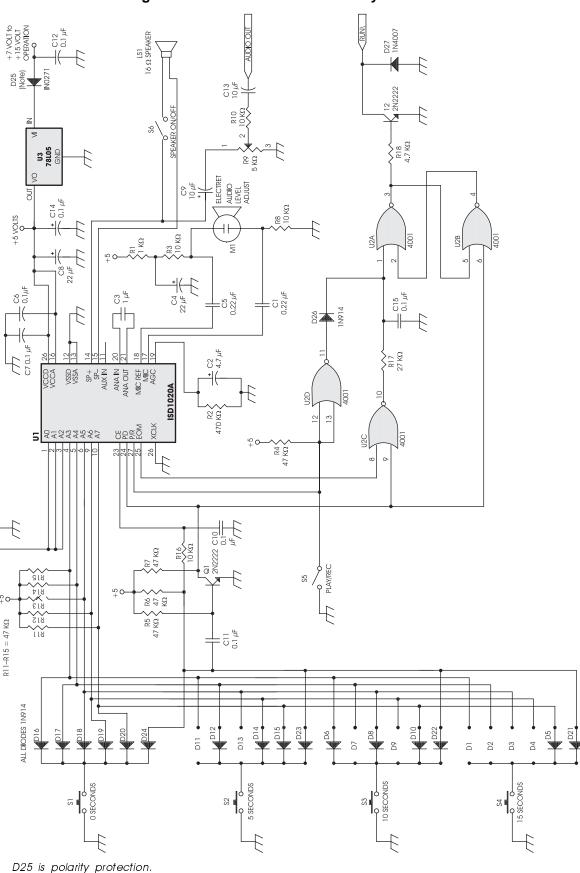

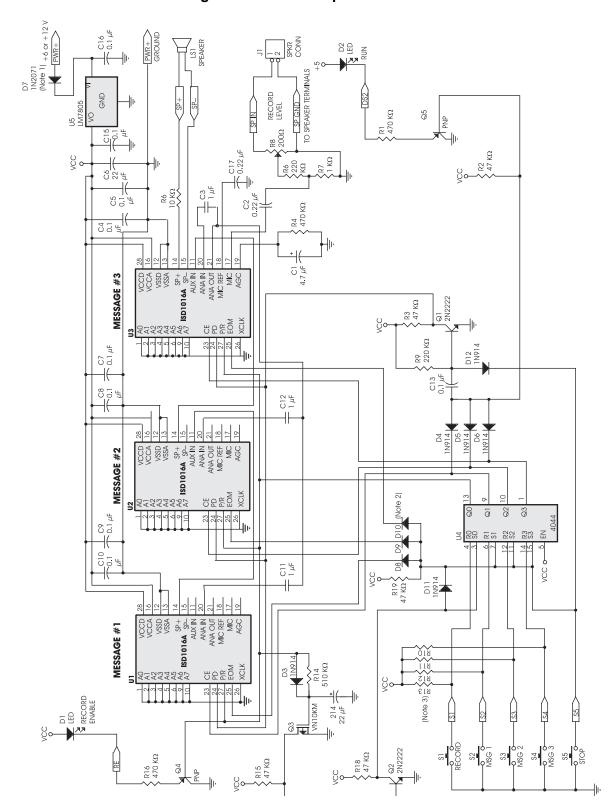

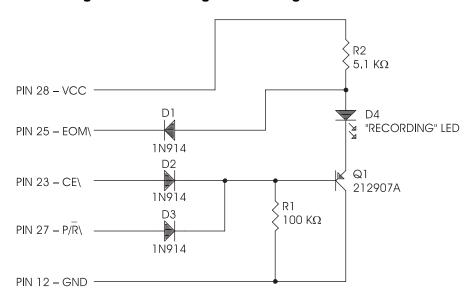

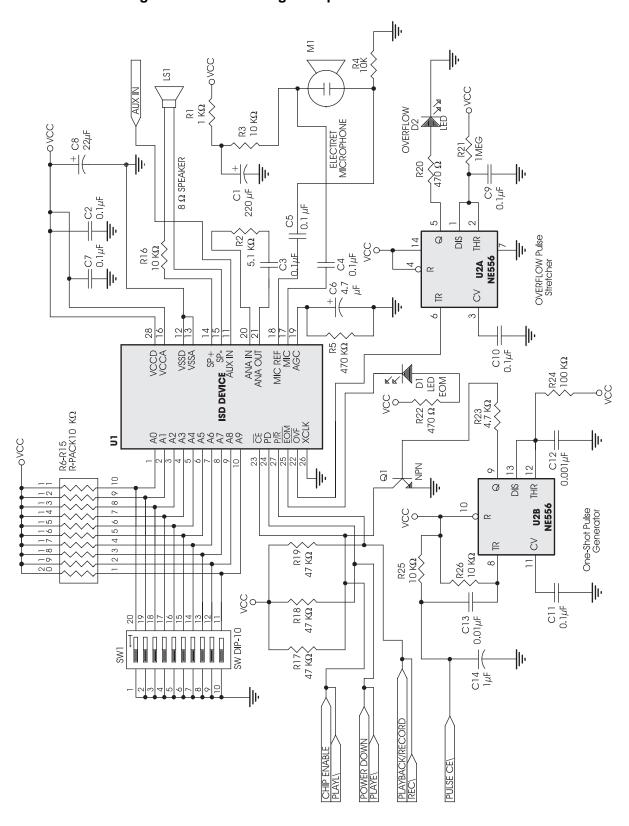

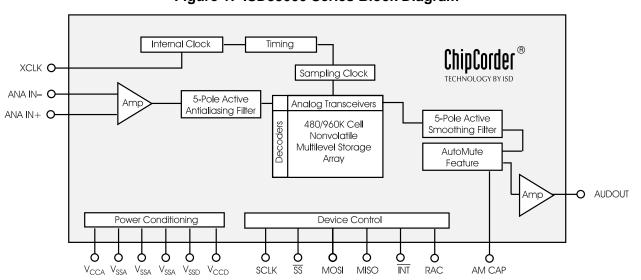

Numerous schematics in the following sections show single-chip voice message systems. A block diagram of one family of ISD devices is shown in Figure 1. In this device, the external components (a microphone, loudspeaker, switches, a few resistors and capacitors, and a power source) are all that is required to build a complete voice record

and playback system. All other functions (preamplifier, filters, AGC, power amplifier, control logic, and analog storage) are performed on-chip. This device, the ISD2500 and other products such as the ISD1100, ISD1200 and ISD1400 families emphasize simple push-button or parallel addressed microcontroller operation from a single 5-volt supply.

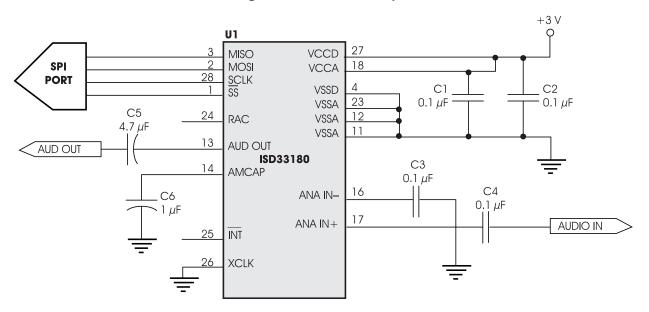

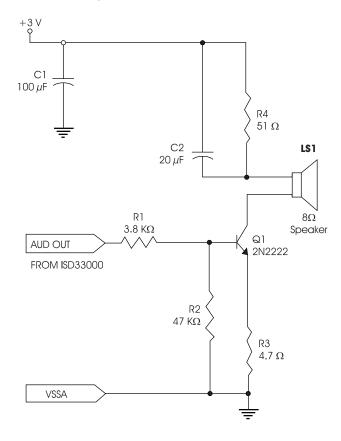

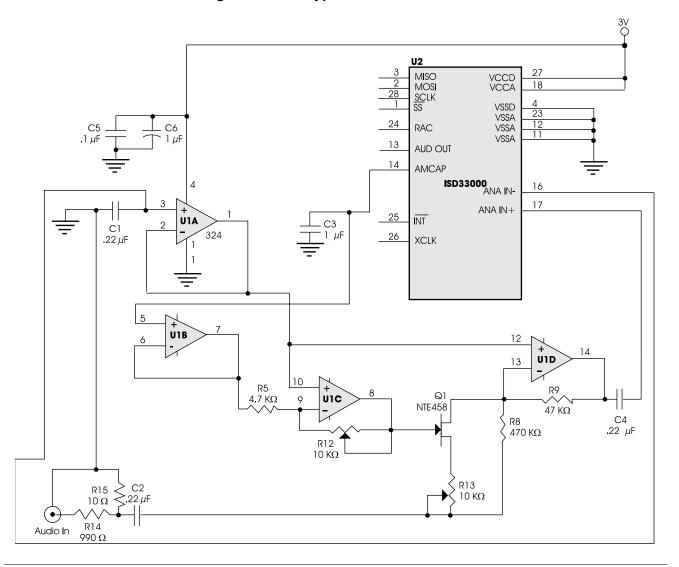

A new series of devices, starting with the ISD33000 family, emphasizes 3 volt operation and serial port control and may be tailored for specific markets. The ISD33000, for instance, does not have the onchip microphone amplifier and speaker driver, allowing for a more cost-effective solution for those applications that already have those functions included elsewhere in the circuit.

Figure 1: ISD2560/75/90/120 Basic Block Diagram

#### **OPERATIONAL OVERVIEW**

During recording, the ISD device performs several stages of signal conditioning before the actual storage operation takes place.

For example, in those products with an included on-chip AGC, the first stages are composed of a preamplifier, amplifier and AGC blocks.

The preamplifier is connected to the microphone by a DC blocking capacitor that removes the DC component from the low level (2 to 20 mV) AC signal. Amplification is performed in two stages; initially by the input preamplifier and then by the fixed gain amplifier. The signal path is completed by connecting a capacitor between the ANA OUT and ANA IN pins.

Such an architecture allows system design flexibility, particularly for non-voice applications and also provides an additional pole for low frequency cutoff. The AGC circuit dynamically monitors the signal level at the amplifier output and sends a gain control voltage to the preamplifier. The preamplifier gain is automatically adjusted to maintain an optimum signal level into the filter. This gives the highest level of recorded signal while reducing clipping to a minimum.

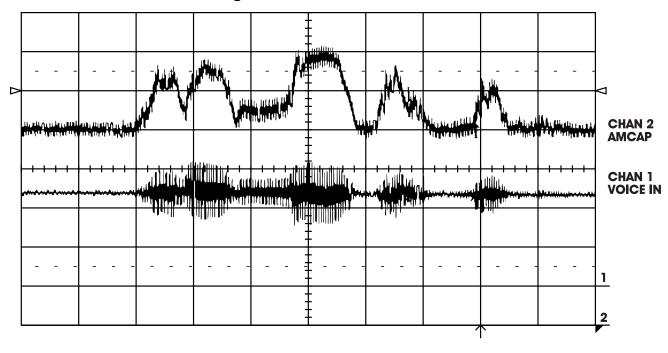

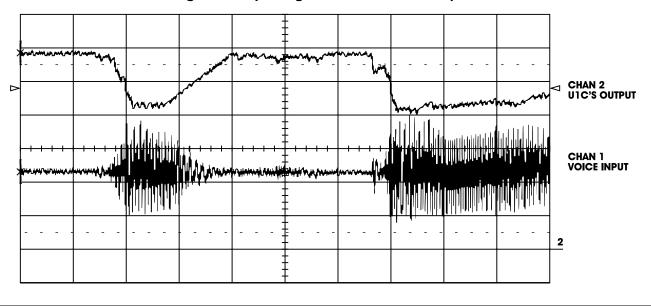

The characteristic of the AGC circuit is described by two time constants; the attack time and the release time.

- Attack time is the time required by the AGC to reduce gain in response to an increasing input signal.

- Release time is the time constant of the gain increase in the presence of a decreasing signal.

The user can adjust both the attack and the release time by selecting values of the resistor and capacitor connected to the AGC pin. Certain default values will give optimum performance for normal speech; however, the accessibility of the resistance and the capacitance allows the user to tailor the AGC to his own particular needs. The 20 dB or so gain compression range on the preamplifier compensates for various microphone characteristics and also various levels of speech volume. The signal integrity is maintained. There is

minimum clipping or other forms of distortion yet the dynamic signal range is increased by 20 dB.

All ISD devices next include a stage of signal conditioning performed by an input filter. As we will see later, the storage, although analog in nature, still employs sampling techniques. As a result the device requires an antialiasing filter to remove (or at least reduce to an insignificant level) input frequency components above half the sampling frequency. This is to satisfy the well-known Nyquist Criterion that applies to all sampled data systems.

Voice quality better than "telephone quality" (telephones cut off below 300 Hz) is achieved with a sampling frequency of 8 KHz. The high frequency cutoff of the low pass filter is then chosen to be 3.4 KHz, satisfying the Nyquist criterion, but still with a wide enough frequency band to allow for good quality voice reproduction. The filter is a continuous time, 5-pole low-pass filter with a roll-off of 40 dB per octave at 3.4 KHz.

Signal conditioning is now completed. The input waveform is then passed into the analog transceivers to be written into the Analog Storage Array. Samples are taken by the 8-KHz sample clock. These samples undergo a level shifting process to produce the high voltages required for the nonvolatile writing procedure, at the same time compensating for some of the practicalities related to Fowler-Nordheim tunneling. The sample clock is also used to increment the array decode so that the input samples are mapped sequentially into the array.

During playback, the recorded analog voltages are sequentially read from the storage array under control of the same sample clock, reconstructing the sampled waveform. The smoothing filter on the output path removes the sampling frequency component and the original waveform is restored.

The frequency of the sample clock affects record duration and quality. As the frequency increases the sound quality is improved, but, of course, the record duration is reduced. Conversely, a lower oscillator frequency gives increased duration at the cost of lower quality. The oscillator frequency

2 Voice Solutions in Silicon<sup>™</sup>

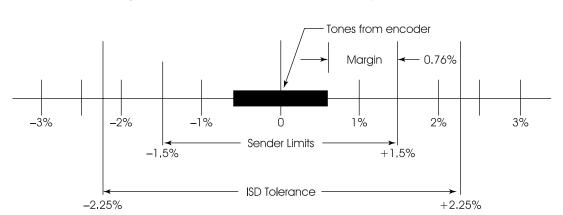

is trimmed to an accuracy better than 1% before the product leaves the factory. This is achieved by taking further advantage of the features of this technology. Trimming of oscillator components is done by programming nonvolatile trim bits that have been included on-chip.

The same process variables that affect the oscillator frequency also effect the filter cutoff frequency. When we trim the oscillator frequency, we also automatically trim the filter cutoff frequency.

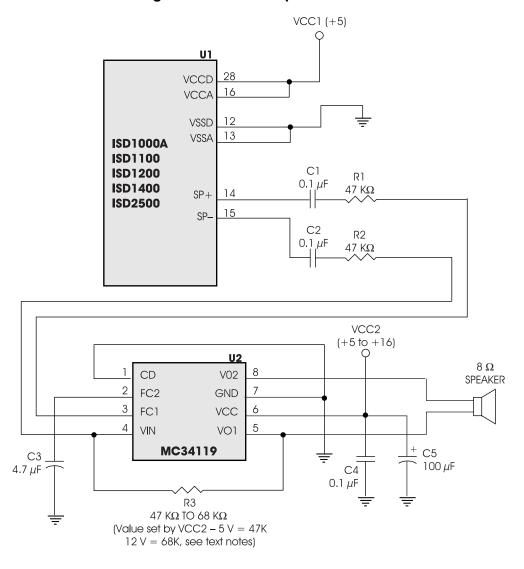

All ISD devices also include a smoothing filter connected to the output of the analog storage array. In devices without an on-chip speaker driver, this filter output is buffered and presented to an output pin.

Some ISD products include an on-chip speaker driver. In these devices, the output of the smoothing filter is connected through an analog multiplexer into the output power amplifier. Two output pins provide direct speaker drive capability of about 12.5 mW RMS (25 mW peak) into a 16 ohm speaker. This is enough to be clearly heard from the other side of a normal sized room. In some products the speaker driver is also available for system use via the AUX IN pin. From this input it can provide 50 mW RMS output.

The circuit design used in the ISD Series of devices results in the equivalent of 8 bits of storage in each EEPROM cell. Information is written into the cell in a closed loop fashion. A sample-and-hold circuit holds the data during the programming cycle and supplies the analog voltage to be stored to one input of a comparator. The other input to the comparator is the output of the storage cell itself. Electrons are pumped into the cell during multiple writes and the resulting stored level is fed back to the comparator.

When the comparator signals that the cell output voltage equals the level from the sample-and-hold, programming of that cell ceases. The minimum amount of charge injected into the cell during each write sets up system resolution. This is approximately 256 levels, which is equivalent to 8 bits of accuracy. Writing to the cell in this manner also eliminates cell to cell variations.

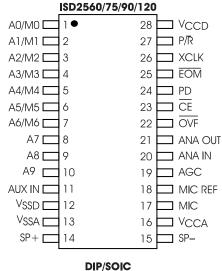

Figure 2: ISD2500 Pinout

The process used is based on the EEPROM floating gate technology. ISD guarantees 10 years of data retention but laboratory tests suggest that the typical data retention will be 100 years.

### APPLICATION INFORMATION FOR ALL ISD ChipCorder PRODUCTS

## **Microphone and Speaker Selection**

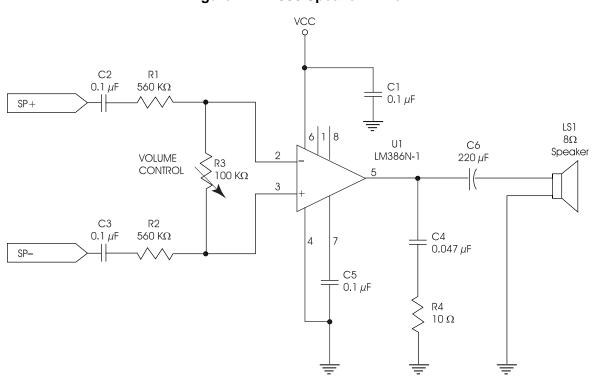

The ISD1000A series data sheet recommends a minimum speaker impedance of 16  $\Omega$ . An 8  $\Omega$  impedance speaker may be used that will result in a higher volume level and increased distortion. In addition, I<sub>CC</sub> current will be higher. An 8 to 20  $\Omega$  resistor, in series with the speaker, controls volume and reduces I<sub>CC</sub> playback current. Additionally, the speaker enclosure is important for best audio performance. Experiment with the sound cavity, grille, and foam baffle behind the speaker to optimize the system's performance.

Volume and audio improvements of 50 to 100 percent can be realized with improvements to the speaker enclosure that can include a sound baffle of foam or glass wool.

It is recommended that the ISD devices be evaluated initially using high quality speakers and low background noise to confirm the high voice quality possible. Then if trade-offs need to be made later on speaker size or quality, an informed quality versus cost decision can be made.

The selection of a good quality microphone and speaker enhances the audio performance of your application.

Two sources for  $16-\Omega$  speakers are:

MCM Electronics Dayton, OH (800) 543-4330

QUAM Chicago, IL (312) 488-5800

With the proper connections, some telephone handsets can also be used. Good quality audio techniques should be used so input signal noise and background noise will be minimized during recording.

**Table 1: Speaker Sources**

| Mfg.    | Device #     | Shape      | Weight    | Freq. Resp. | Max. Watts |

|---------|--------------|------------|-----------|-------------|------------|

| Quam    | 4A1Z16       | 3" sq.     | 0,25 lbs. | 200–11K     | 3          |

| Quam    | 35A05Z16     | 3 x 5 oval | 0.50 lbs. | 150–7K      | 2          |

| Pioneer | ALLEC80-092F | 4.5" round | 1,50 lbs. | 68–15K      | 30         |

## MICROPHONE OPTIONS FOR THE ISD1000A, ISD1100, ISD1200, ISD1400, ISD1500, AND ISD2500 SERIES

Most schematics for the ISD single-chip voice record and playback devices show the use of a conventional electret or "capacitor" microphone. These microphones have several advantages over other common types. They have excellent frequency response and high output. They are available in many different sizes, from "grain-of-rice" to a standard 1/4-inch diameter. They are also rugged and inexpensive.

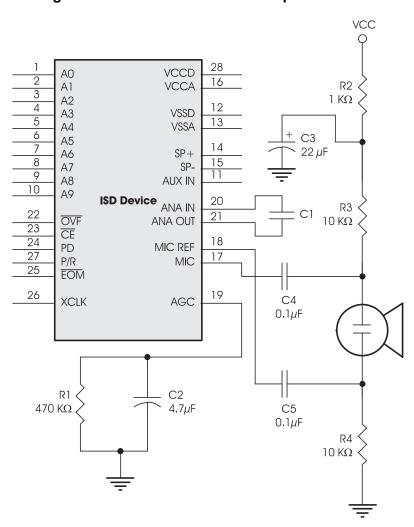

The ISD "standard" microphone application requires seven components to operate; see Figure 1. These components perform several functions.

- Microphone bias is supplied by a network composed of R2, R3, and R4, with C3 acting as a filter capacitor.

- C4 is a DC blocking capacitor between the microphone and the MIC pin on the ISD device.

- C5 acts as a coupling capacitor bringing microphone ground noise into the MIC REF pin.

- The MIC REF input provides a noise canceling (common mode rejection) input to reduce recorded noise.

- Since R3 and R4 are equal, the power supply noise will be equal and canceled by the common mode rejection of the microphone preamplifier.

These parts must be used with any microphone that requires DC bias. Another example would be a carbon microphone. These were used until recently in telephones or two way radios. However, there are other microphones that do not require a bias supply.

There are several types of microphones that are "self-generating." These microphones cause a current to flow (or a potential to be developed) directly from sound wave pressure. Two of these are dynamic and crystal microphones.

- A dynamic microphone uses a coil of wire and a magnet. One end of the magnet is tied to a diaphragm to generate a current proportional to sound pressure.

- A crystal microphone has a diaphragm connected to a crystalline structure. Sound pressure causes stress in the crystal. Through the piezoelectric effect the crystal generates a voltage.

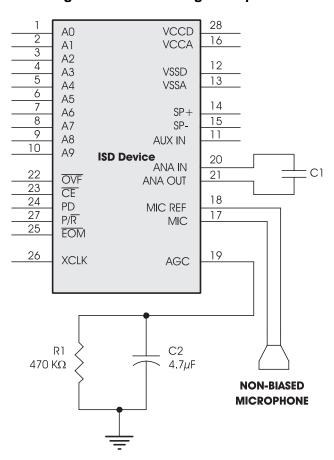

Such self-generating microphones may be connected directly to an ISD device's microphone inputs.

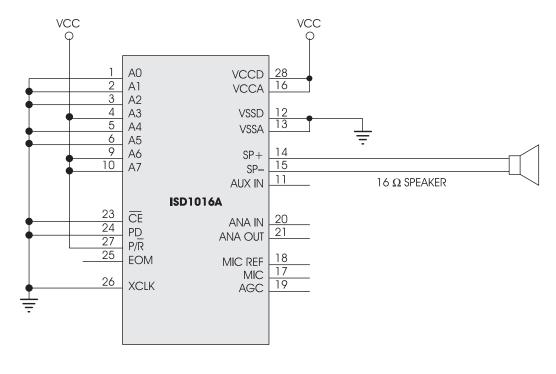

The two microphone inputs to the ISD device are MIC and MIC REF. These two pins are differential inputs to the on-chip microphone preamplifier. A non-biased microphone, as discussed, may be connected directly across these two pins. No coupling capacitors are needed. This benefits the designer in several ways. Most obvious is the elimination of the components associated with the microphone bias. The secondary considerations may be as important.

Figure 2 shows how a non-biased microphone is connected to an ISD single-chip voice record/playback device. Only the components directly associated with the microphone are shown.

When an electret microphone is used, its signal must be referenced to the external circuit ground. This is because of the bias requirement. This creates two potential external sources of noise. Noise can come from the  $V_{CC}$  supply and from currents flowing in the circuit board ground.

The MIC REF pin is a common mode noise canceling input in the electret application. This method of noise reduction usually works well. It depends on good PC board layout rules and adequate bypassing of the  $V_{\rm CCD}$  and  $V_{\rm CCA}$  pins. When a non-biased microphone is used, however, these two noise sources are eliminated. A designer may find the circuit will perform adequately with no bypass capacitors at all.

2 Voice Solutions in Silicon<sup>™</sup>

Several readily available microphones will drive ISD1000A, ISD1100, ISD1200, ISD1400 ISD1500, and ISD2500 series devices. The following notes have been determined experimentally from a sample of microphone elements.

- Crystal, ceramic, and dynamic microphone elements (as well as crystal earphones) will work when connected directly to the MIC and MIC REF inputs of ISD devices.

- In general, the crystal and dynamic microphones have more output level and the ceramic elements less.

- The best quality was achieved using the dynamic microphone.

- A piezo speaker element (sometimes called a sounder) will work adequately for some applications. It must be mechanically mounted to some sort of sounding board (such as a piece of cardboard). The cardboard becomes a sounding board and couples the sound pressure into the element. Note that piezo sounders come in active and passive styles. The active piezo elements are actually noise makers and cannot be used as microphones.

Catalog suppliers such as Mouser (1-800-346-6873) carry microphone elements of several types that will work adequately. The Mouser catalog shows electret, crystal, ceramic, and dynamic microphones plus crystal earphones.

One source for piezo speaker elements is Radio Shack (part number is 273-091).

#### **ELECTRET MICROPHONE SPECIFICATIONS**

Specifications for the electret microphone are:

- · 1 K $\Omega$  impedence

- Omni-directional

- 64 dB sensitivity

- 50 Hz to 8 KHz frequency

- Less than 1 mA current drain

- Greater than 40 dB S/N ratio

- Operates 2 to 10 VDC

These microphone specifications are not critical; however, microphones with these characteristics have been found to operate satisfactory.

Three sources for electret microphones are:

Mouser Electronics (800) 346-6873 #25LM049 (PC mount) #25LM045 (Coax leads)

Radio Shack (800) 433-2024 #270-090 (PC mount) #270-092 (Coax leads) #273-091 (Piezo)

DIGI-KEY (800) 344-4539 #P9931-ND (PC mount)

#### PREFERRED ELECTRET MICROPHONE CIRCUIT

Figure 1 shows a differential circuit for the standard ISD device microphone input. In this circuit, an electret microphone is used to differentially drive the microphone preamplifier. The microphone is connected directly between MIC and MIC REF. Since R3 and R4 are equal resistors, power supply noise will be a common mode signal. Common mode rejection inherent in the microphone preamplifier will attenuate any noise.

Figure 1: Differential Electret Microphone Circuit

Figure 2: Self-Biasing Microphone

## APPLICATION INFORMATION FOR ALL ISD ChipCorder PRODUCTS Address Segment Resolution

|     |                     |                   |    |    |       |           |      |    |           |    |     |         |         |         | Samp    | le Rates | ;       |         |         |

|-----|---------------------|-------------------|----|----|-------|-----------|------|----|-----------|----|-----|---------|---------|---------|---------|----------|---------|---------|---------|

|     |                     |                   |    |    |       |           |      |    |           |    |     | 8.0 KHz | 6.4 KHz | 5.3 KHz | 4.0 KHz | 8.0 KHz  | 6.4 KHz | 5.3 KHz | 4.0 KHz |

|     |                     |                   |    |    |       |           |      |    |           |    |     |         |         |         | ISD Par | t Numbe  | ers     |         |         |

|     |                     |                   |    |    |       |           |      |    |           |    |     |         | 1110    |         |         |          |         |         |         |

|     |                     |                   |    |    |       |           |      |    |           |    |     |         | 1210    | 1212    |         |          |         |         |         |

|     |                     |                   |    |    |       |           |      |    |           |    |     | 1016A   | 1020A   |         |         |          |         |         |         |

|     |                     |                   |    |    |       |           |      |    |           |    |     | 1416    | 1420    |         |         |          |         |         |         |

|     |                     |                   |    | A  | Addre | ess Ir    | puts | ;  |           |    |     | 2532    | 2540    | 2548    | 2564    | 33060    | 33075   | 33090   | 33120-4 |

| DEC | A9                  | <b>A8</b>         | A7 | A6 | A5    | <b>A4</b> | А3   | A2 | <b>A1</b> | A0 |     | 2560    | 2575    | 2590    | 25120   | 33120    | 33150   | 33180   | 33240   |

| 0   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 0  | 0         | 0  | 0 0 | 0       | 0       | 0       | 0       | 0        | 0       | 0       | 0       |

| 1   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 0  | 0         | 1  | 0 1 | 0.1     | 0.125   | 0.15    | 0.2     | 0.15     | 0.1875  | 0.225   | 0.3     |

| 2   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 0  | 1         | 0  | 0 2 | 0.2     | 0.25    | 0.3     | 0.4     | 0.3      | 0.375   | 0.45    | 0.6     |

| 3   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 0  | 1         | 1  | 0 3 | 0.3     | 0.375   | 0.45    | 0.6     | 0.45     | 0.5625  | 0.675   | 0.9     |

| 4   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 1  | 0         | 0  | 0 4 | 0.4     | 0.5     | 0.6     | 0.8     | 0.6      | 0.75    | 0.9     | 1.2     |

| 5   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 1  | 0         | 1  | 0 5 | 0.5     | 0.625   | 0.75    | 1       | 0.75     | 0.9375  | 1.125   | 1.5     |

| 6   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 1  | 1         | 0  | 0 6 | 0.6     | 0.75    | 0.9     | 1.2     | 0.9      | 1.125   | 1.35    | 1.8     |

| 7   | 0                   | 0                 | 0  | 0  | 0     | 0         | 0    | 1  | 1         | 1  | 0 7 | 0.7     | 0.875   | 1.05    | 1.4     | 1.05     | 1.3125  | 1.575   | 2.1     |

| 8   | 0                   | 0 0 0 0 0 0 1 0 0 |    |    |       |           |      |    |           |    |     | 0.8     | 1       | 1.2     | 1.6     | 1.2      | 1.5     | 1.8     | 2.4     |

| 9   | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 0  | 0         | 1  | 0 9 | 0.9     | 1.125   | 1.35    | 1.8     | 1.35     | 1.6875  | 2.025   | 2.7     |

| 10  | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 0  | 1         | 0  | 0 A | 1       | 1.25    | 1.5     | 2       | 1.5      | 1.875   | 2.25    | 3       |

| 11  | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 0  | 1         | 1  | ОВ  | 1.1     | 1.375   | 1.65    | 2.2     | 1.65     | 2.0625  | 2.475   | 3.3     |

| 12  | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 1  | 0         | 0  | 0 C | 1.2     | 1.5     | 1.8     | 2.4     | 1.8      | 2.25    | 2.7     | 3.6     |

| 13  | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 1  | 0         | 1  | 0 D | 1.3     | 1.625   | 1.95    | 2.6     | 1.95     | 2.4375  | 2.925   | 3.9     |

| 14  | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 1  | 1         | 0  | 0 E | 1.4     | 1.75    | 2.1     | 2.8     | 2.1      | 2.625   | 3.15    | 4.2     |

| 15  | 0                   | 0                 | 0  | 0  | 0     | 0         | 1    | 1  | 1         | 1  | O F | 1.5     | 1.875   | 2.25    | 3       | 2.25     | 2.8125  | 3.375   | 4.5     |

| 16  | 0                   | 0                 | 0  | 0  | 0     | 1         | 0    | 0  | 0         | 0  | 1 0 | 1.6     | 2       | 2.4     | 3.2     | 2.4      | 3       | 3.6     | 4.8     |

| 17  | 0                   | 0 0 0 0 0 1 0 0 0 |    |    |       |           |      |    |           | 1  | 1 1 | 1.7     | 2.125   | 2.55    | 3.4     | 2.55     | 3.1875  | 3.825   | 5.1     |

| 18  | 0 0 0 0 0 1 0 0 1   |                   |    |    |       |           |      |    |           |    | 1 2 | 1.8     | 2.25    | 2.7     | 3.6     | 2.7      | 3.375   | 4.05    | 5.4     |

| 19  | 0 0 0 0 0 1 0 0 1 1 |                   |    |    |       |           |      |    |           |    |     | 1.9     | 2.375   | 2.85    | 3.8     | 2.85     | 3,5625  | 4.275   | 5.7     |

| 20  | 0                   | 0                 | 0  | 0  | 0     | 1         | 0    | 1  | 0         | 0  | 1 4 | 2       | 2.5     | 3       | 4       | 3        | 3.75    | 4.5     | 6       |

| 21  | 0                   | 0                 | 0  | 0  | 0     | 1         | 0    | 1  | 0         | 1  | 1 5 | 2.1     | 2.625   | 3.15    | 4.2     | 3.15     | 3.9375  | 4.725   | 6.3     |

| 22  | 0                   | 0                 | 0  | 0  | 0     | 1         | 0    | 1  | 1         | 0  | 1 6 | 2.2     | 2.75    | 3.3     | 4.4     | 3.3      | 4.125   | 4.95    | 6.6     |

| 23  | 0                   | 0                 | 0  | 0  | 0     | 1         | 0    | 1  | 1         | 1  | 1 7 | 2.3     | 2.875   | 3.45    | 4.6     | 3.45     | 4.3125  | 5.175   | 6.9     |

|                 |    |    |    |    |      |        |      |          |           |    |     |            |         |             | Samp    | le Rates    | i              |         |              |

|-----------------|----|----|----|----|------|--------|------|----------|-----------|----|-----|------------|---------|-------------|---------|-------------|----------------|---------|--------------|

|                 |    |    |    |    |      |        |      |          |           |    |     | 8.0 KHz    | 6.4 KHz | 5.3 KHz     |         |             | 6.4 KHz        | 5.3 KHz | 4.0 KHz      |

|                 |    |    |    |    |      |        |      |          |           |    |     |            |         |             | ISD Par | t Numbe     | rs             |         |              |

|                 |    |    |    |    |      |        |      |          |           |    |     |            | 1110    |             |         |             |                |         |              |

|                 |    |    |    |    |      |        |      |          |           |    |     |            | 1210    | 1212        |         |             |                |         |              |

|                 |    |    |    |    |      |        |      |          |           |    |     | 1016A      | 1020A   |             |         |             |                |         |              |

|                 |    |    |    |    |      |        |      |          |           |    |     | 1416       | 1420    |             |         |             |                |         |              |

| ſ               |    |    |    | Δ  | ddre | ess Ir | puts | <b>;</b> |           |    |     | 2532       | 2540    | 2548        | 2564    | 33060       | 33075          | 33090   | 33120-4      |

| DEC             | A9 | A8 | A7 | A6 | A5   | A4     | A3   | A2       | <b>A1</b> | Α0 |     | 2560       | 2575    | 2590        | 25120   | 33120       | 33150          | 33180   | 33240        |

| 24              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 0        | 0         | 0  | 1 8 | 2.4        | 3       | 3.6         | 4.8     | 3.6         | 4.5            | 5.4     | 7.2          |

| 25              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 0        | 0         | 1  | 1 9 | 2.5        | 3.125   | 3.75        | 5       | 3.75        | 4.6875         | 5.625   | 7.5          |

| 26              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 0        | 1         | 0  | 1 A | 2.6        | 3.25    | 3.9         | 5.2     | 3.9         | 4.875          | 5.85    | 7.8          |

| 27              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 0        | 1         | 1  | 1 B | 2.7        | 3,375   | 4.05        | 5.4     | 4.05        | 5.0625         | 6.075   | 8.1          |

| 28              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 1        | 0         | 0  | 1 C | 2.8        | 3.5     | 4.2         | 5.6     | 4.2         | 5.25           | 6.3     | 8.4          |

| 29              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 1        | 0         | 1  | 1 D | 2.9        | 3,625   | 4.35        | 5,8     | 4.35        | 5.4375         | 6.525   | 8.7          |

| 30              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 1        | 1         | 0  | 1 E | 3          | 3.75    | 4.5         | 6       | 4.5         | 5.625          | 6.75    | 9            |

| 31              | 0  | 0  | 0  | 0  | 0    | 1      | 1    | 1        | 1         | 1  | 1 F | 3.1        | 3.875   | 4.65        | 6.2     | 4.65        | 5.8125         | 6.975   | 9.3          |

| 32              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 0        | 0         | 0  | 2 0 | 3.2        | 4       | 4.8         | 6.4     | 4.8         | 6              | 7.2     | 9.6          |

| 33              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 0        | 0         | 1  | 2 1 | 3.3        | 4.125   | 4.95        | 6.6     | 4.95        | 6.1875         | 7.425   | 9.9          |

| 34              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 0        | 1         | 0  | 2 2 | 3.4        | 4.25    | 5.1         | 6.8     | 5.1         | 6.375          | 7.65    | 10.2         |

| 35              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 0        | 1         | 1  | 2 3 | 3.5        | 4.375   | 5.25        | 7       | 5.25        | 6.5625         | 7.875   | 10.5         |

| 36              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 1        | 0         | 0  | 2 4 | 3.6        | 4.5     | 5.4         | 7.2     | 5.4         | 6.75           | 8.1     | 10.8         |

| 37              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 1        | 0         | 1  | 2 5 | 3.7        | 4.625   | 5.55        | 7.4     | 5.55        | 6.9375         | 8.325   | 11.1         |

| 38              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 1        | 1         | 0  | 2 6 | 3.8        | 4.75    | 5.7         | 7.6     | 5.7         | 7.125          | 8.55    | 11.4         |

| 39              | 0  | 0  | 0  | 0  | 1    | 0      | 0    | 1        | 1         | 1  | 2 7 | 3.9        | 4.875   | 5.85        | 7.8     | 5.85        | 7.3125         | 8.775   | 11.7         |

| 40              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 0        | 0         | 0  |     | 4          | 5       | 6           | 8       | 6           | 7.5            | 9       | 12           |

| 41              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 0        | 0         | 1  | 2 9 | 4.1        | 5.125   | 6.15        | 8.2     | 6.15        | 7.6875         | 9.225   | 12.3         |

| 42              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 0        | 1         | 0  | 2 A | 4.2        | 5.25    | 6.3         | 8.4     | 6.3         | 7.875          | 9.45    | 12.6         |

| 43              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 0        | 1         | 1  | 2 B | 4.3        | 5,375   | 6.45        | 8,6     | 6.45        | 8.0625         | 9.675   | 12.9         |

| 44              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 1        | 0         | 0  | 2 C | 4.4        | 5.5     | 6.6         | 8.8     | 6.6         | 8.25           | 9.9     | 13.2         |

| 45              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 1        | 0         | 1  | 2 D |            | 5.625   | 6.75        | 9       | 6.75        | 8.4375         | 10.125  | 13.5         |

| 46              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 1        | 1         |    | 2 E | 4.6        | 5.75    | 6.9         | 9.2     | 6.9         | 8.625          | 10.35   | 13.8         |

| 47              | 0  | 0  | 0  | 0  | 1    | 0      | 1    | 1        | 1         | 1  |     | 4.7        | 5.875   | 7.05        | 9.4     | 7.05        | 8.8125         | 10,575  | 14.1         |

| 48              | 0  | 0  | 0  | 0  | 1    | 1      | 0    | 0        | 0         | 0  |     | 4.8        | 6       | 7.2         | 9.6     | 7.2         | 9              | 10.8    | 14.4         |

| 49              | 0  | 0  | 0  | 0  | 1    | 1      | 0    | 0        | 0         | 1  | 3 1 | 4.9        | 6.125   | 7.35        | 9.8     | 7.35        | 9.1875         | 11.025  | 14.7         |

| 50              | 0  | 0  | 0  | 0  | 1    | 1      | 0    | 0        | 1         | 0  |     | 5          | 6.25    | 7.5         | 10      | 7.5         | 9.375          | 11.25   | 15           |

| 51              | 0  | 0  | 0  | 0  | 1    | 1      | 0    | 0        | 1         | 1  | 3 3 | 5.1        | 6.375   | 7.65        | 10.2    | 7.65        | 9.5625         | 11.475  | 15.3         |

| 52<br>53        | 0  | 0  | 0  |    |      | 1      | 0    | 1        | 0         | 0  | 3 4 | 5.2<br>5.3 | 6.5     | 7.8         | 10.4    | 7.8         | 9.75<br>9.9375 | 11.7    | 15.6<br>15.9 |

| 54              | 0  | 0  | 0  | 0  | 1    | 1      | 0    | 1        | 0         | 0  |     | 5.4        | 6.75    | 7.95<br>8.1 | 10.8    | 7.95<br>8.1 | 10.125         | 11.925  | 16.2         |

| 55              | 0  | 0  | 0  | 0  | 1    | 1      | 0    | 1        | 1         | 1  | 3 7 | 5.5        | 6.875   | 8.25        | 10.8    | 8.25        | 10.3125        | 12.13   | 16.2         |

| 56              | 0  | 0  | 0  | 0  | 1    | 1      | 1    | 0        | 0         | 0  |     | 5.6        | 7       | 8.4         | 11.2    | 8.4         | 10.3123        | 12.575  | 16.8         |

| 57              | 0  | 0  | 0  | 0  | 1    | 1      | 1    | 0        | 0         | 1  | 3 9 | 5.7        | 7.125   | 8.55        | 11.4    | 8.55        | 10.6875        | 12.825  | 17.1         |

| 58              | 0  | 0  | 0  | 0  | 1    | 1      | 1    | 0        | 1         | 0  |     | 5.8        | 7.25    | 8.7         | 11.4    | 8.7         | 10.875         | 13.05   | 17.1         |

| <del>- 59</del> | 0  | 0  | 0  | 0  | 1    | 1      | 1    | 0        | 1         | 1  | 3 B | 5.9        | 7 375   | 8.85        | 11.8    | 8.85        | 11.0625        | 13.275  | 17.7         |

| 60              | 0  | 0  | 0  | 0  | 1    | 1      | 1    | 1        | 0         | 0  | 3 C | 6          | 7.5     | 9           | 12      | 9           | 11.25          | 13.5    | 17.7         |

| 00              | J  | U  | U  | U  | I    | I      |      |          | U         | U  | 5   | O          | 7.3     | 9           | 12      | 9           | 11.23          | 10.0    | 10           |

|     |           |           |    |    |           |    |       |    |           |    |     |         |         |         | Samp    | le Rates |         |         |         |

|-----|-----------|-----------|----|----|-----------|----|-------|----|-----------|----|-----|---------|---------|---------|---------|----------|---------|---------|---------|

|     |           |           |    |    |           |    |       |    |           |    |     | 8.0 KHz | 6.4 KHz | 5.3 KHz | 4.0 KHz | 8.0 KHz  | 6.4 KHz | 5.3 KHz | 4.0 KHz |

|     |           |           |    |    |           |    |       |    |           |    |     |         |         |         | ISD Par | t Numbe  | rs      |         |         |

|     |           |           |    |    |           |    |       |    |           |    |     |         | 1110    |         |         |          |         |         |         |

|     |           |           |    |    |           |    |       |    |           |    |     |         | 1210    | 1212    |         |          |         |         |         |

|     |           |           |    |    |           |    |       |    |           |    |     | 1016A   | 1020A   |         |         |          |         |         |         |

|     |           |           |    |    |           |    |       |    |           |    |     | 1416    | 1420    |         |         |          |         |         |         |

|     |           |           |    | A  | Addre     |    | nputs | 3  |           |    |     | 2532    | 2540    | 2548    | 2564    | 33060    | 33075   | 33090   | 33120-4 |

| DEC | <b>A9</b> | <b>A8</b> | A7 | A6 | <b>A5</b> | A4 | А3    | A2 | <b>A1</b> | A0 |     | 2560    | 2575    | 2590    | 25120   | 33120    | 33150   | 33180   | 33240   |

| 61  | 0         | 0         | 0  | 0  | 1         | 1  | 1     | 1  | 0         |    | 3 D | 6.1     | 7.625   | 9.15    | 12.2    | 9.15     | 11.4375 | 13.725  | 18.3    |

| 62  | 0         | 0         | 0  | 0  | 1         | 1  | 1     | 1  | 1         |    | 3 E | 6.2     | 7.75    | 9.3     | 12.4    | 9.3      | 11.625  | 13.95   | 18.6    |

| 63  | 0         | 0         | 0  | 0  | 1         | 1  | 1     | 1  | 1         |    | 3 F | 6.3     | 7.875   | 9.45    | 12.6    | 9.45     | 11.8125 | 14.175  | 18.9    |

| 64  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 0  | 0         |    | 4 0 |         | 8       | 9.6     | 12.8    | 9.6      | 12      | 14.4    | 19.2    |

| 65  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 0  | 0         |    | 4 1 | 6.5     | 8.125   | 9.75    | 13      | 9.75     | 12.1875 | 14.625  | 19.5    |

| 66  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 0  | 1         | 0  | 4 2 |         | 8.25    | 9.9     | 13.2    | 9.9      | 12.375  | 14.85   | 19.8    |

| 67  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 0  | 1         | 1  | 4 3 | 6.7     | 8.375   | 10.05   | 13.4    | 10.05    | 12.5625 | 15.075  | 20.1    |

| 68  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 1  | 0         | 0  | 4 4 | 6.8     | 8.5     | 10.2    | 13.6    | 10.2     | 12.75   | 15.3    | 20.4    |

| 69  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 1  | 0         | 1  | 4 5 |         | 8.625   | 10.35   | 13.8    | 10.35    | 12.9375 | 15.525  | 20.7    |

| 70  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 1  | 1         |    | 4 6 |         | 8.75    | 10.5    | 14      | 10.5     | 13.125  | 15.75   | 21      |

| 71  | 0         | 0         | 0  | 1  | 0         | 0  | 0     | 1  | 1         |    | 4 7 | 7.1     | 8.875   | 10.65   | 14.2    | 10.65    | 13.3125 | 15.975  | 21.3    |

| 72  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 0  | 0         | 0  | 4 8 |         | 9       | 10.8    | 14.4    | 10.8     | 13.5    | 16.2    | 21.6    |

| 73  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 0  | 0         | 1  | 4 9 |         | 9.125   | 10.95   | 14.6    | 10.95    | 13.6875 | 16.425  | 21.9    |

| 74  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 0  | 1         |    | 4 A | 7.4     | 9.25    | 11.1    | 14.8    | 11.1     | 13.875  | 16.65   | 22.2    |

| 75  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 0  | 1         |    | 4 B | 7.5     | 9.375   | 11.25   | 15      | 11.25    | 14.0625 | 16.875  | 22.5    |

| 76  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 1  | 0         | 0  | 4 C | 7.6     | 9.5     | 11.4    | 15.2    | 11.4     | 14.25   | 17.1    | 22.8    |

| 77  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 1  | 0         | 1  | 4 D |         | 9.625   | 11.55   | 15.4    | 11.55    | 14.4375 | 17.325  | 23.1    |

| 78  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 1  | 1         | 0  | 4 E | 7.8     | 9.75    | 11.7    | 15.6    | 11.7     | 14.625  | 17.55   | 23.4    |

| 79  | 0         | 0         | 0  | 1  | 0         | 0  | 1     | 1  | 1         | 1  | 4 F | 7.9     | 9.875   | 11.85   | 15.8    | 11.85    | 14.8125 | 17.775  | 23.7    |

"End of Message Storage Space for ISD1110, ISD1210, and ISD1212 Devices"

|     |    |           |    |    |       |        |      |    |           |    |     |            |         |            | Sam        | ple Rate | S       |         |         |

|-----|----|-----------|----|----|-------|--------|------|----|-----------|----|-----|------------|---------|------------|------------|----------|---------|---------|---------|

|     |    |           |    |    |       |        |      |    |           |    |     | 8.0<br>KHz | 6.4 KHz | 5.3<br>KHz | 4.0<br>KHz | 8.0 KHz  | 6.4 KHz | 5.3 KHz | 4.0 KHz |

|     |    |           |    |    |       |        |      |    |           |    |     |            |         |            | ISD Pa     | art Numb | ers     |         |         |

|     |    |           |    |    |       |        |      |    |           |    |     | 1016A      | 1020A   |            |            |          |         |         |         |

|     |    |           |    |    |       |        |      |    |           |    |     | 1416       | 1420    |            |            |          |         |         |         |

|     |    |           |    | -  | Addre | ess Ir | puts | ;  |           |    |     | 2532       | 2540    | 2548       | 2564       | 33060    | 33075   | 33090   | 33120-4 |

| DEC | A9 | <b>A8</b> | A7 | A6 | A5    | A4     | А3   | A2 | <b>A1</b> | A0 |     | 2560       | 2575    | 2590       | 25120      | 33120    | 33150   | 33180   | 33240   |

| 80  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 0  | 0         | 0  | 5 0 | 8          | 10      | 12         | 16         | 12       | 15      | 18      | 24      |

| 81  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 0  | 0         | 1  | 5 1 | 8.1        | 10.125  | 12.15      | 16.2       | 12.15    | 15.1875 | 18.225  | 24.3    |

| 82  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 0  | 1         | 0  | 5 2 | 8.2        | 10.25   | 12.3       | 16.4       | 12.3     | 15.375  | 18.45   | 24.6    |

| 83  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 0  | 1         | 1  | 5 3 | 8.3        | 10.375  | 12.45      | 16.6       | 12.45    | 15.5625 | 18.675  | 24.9    |

| 84  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 1  | 0         | 0  | 5 4 | 8.4        | 10.5    | 12.6       | 16.8       | 12.6     | 15.75   | 18.9    | 25.2    |

| 85  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 1  | 0         | 1  | 5 5 | 8.5        | 10.625  | 12.75      | 17         | 12.75    | 15.9375 | 19.125  | 25.5    |

| 86  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 1  | 1         | 0  | 5 6 | 8.6        | 10.75   | 12.9       | 17.2       | 12.9     | 16.125  | 19.35   | 25.8    |

| 87  | 0  | 0         | 0  | 1  | 0     | 1      | 0    | 1  | 1         | 1  | 5 7 | 8.7        | 10.875  | 13.05      | 17.4       | 13.05    | 16.3125 | 19.575  | 26.1    |

| 88  | 0  | 0         | 0  | 1  | 0     | 1      | 1    | 0  | 0         | 0  | 5 8 | 8.8        | 11      | 13.2       | 17.6       | 13.2     | 16.5    | 19.8    | 26.4    |

| 89  | 0  | 0         | 0  | 1  | 0     | 1      | 1    | 0  | 0         | 1  | 5 9 | 8.9        | 11.125  | 13.35      | 17.8       | 13.35    | 16.6875 | 20.025  | 26.7    |

| 90  | 0  | 0         | 0  | 1  | 0     | 1      | 1    | 0  | 1         | 0  | 5 A | 9          | 11.25   | 13.5       | 18         | 13.5     | 16.875  | 20.25   | 27      |

| 91  |    |           |    |    |       |        |      |    |           |    | 5 B | 9.1        | 11.375  | 13.65      | 18.2       | 13.65    | 17.0625 | 20.475  | 27.3    |

| 92  | 0  | 0         | 0  | 1  | 0     | 1      | 1    | 1  | 0         | 0  | 5 C | 9.2        | 11.5    | 13.8       | 18.4       | 13.8     | 17.25   | 20.7    | 27.6    |

| 93  |    |           |    |    |       |        |      |    |           |    | 5 D | 9.3        | 11.625  | 13.95      | 18.6       | 13.95    | 17.4375 | 20.925  | 27.9    |

| 94  | 0  | 0         | 0  | 1  | 0     | 1      | 1    | 1  | 1         | 0  | 5 E | 9.4        | 11.75   | 14.1       | 18.8       | 14.1     | 17.625  | 21.15   | 28.2    |

| 95  | 0  | 0         | 0  | 1  | 0     | 1      | 1    | 7  | 1         | 1  | 5 F | 9.5        | 11.875  | 14.25      | 19         | 14.25    | 17.8125 | 21.375  | 28.5    |

| 96  | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 0  | 0         | 0  | 6 0 | 9.6        | 12      | 14.4       | 19.2       | 14.4     | 18      | 21.6    | 28.8    |

| 97  | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 0  | 0         | 1  | 6 1 | 9.7        | 12.125  | 14.55      | 19.4       | 14.55    | 18.1875 | 21.825  | 29.1    |

| 98  | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 0  | 1         | 0  | 6 2 | 9.8        | 12.25   | 14.7       | 19.6       | 14.7     | 18.375  | 22.05   | 29.4    |

| 99  | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 0  | 1         | 1  | 6 3 | 9.9        | 12.375  | 14.85      | 19.8       | 14.85    | 18.5625 | 22.275  | 29.7    |

| 100 | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 1  | 0         | 0  | 6 4 | 10         | 12.5    | 15         | 20         | 15       | 18.75   | 22.5    | 30      |

| 101 | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 1  | 0         | 1  | 6 5 | 10.1       | 12.625  | 15.15      | 20.2       | 15.15    | 18.9375 | 22.725  | 30.3    |

| 102 | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 1  | 1         |    | 6 6 |            | 12.75   | 15.3       | 20.4       | 15.3     | 19.125  | 22.95   | 30.6    |

| 103 | 0  | 0         | 0  | 1  | 1     | 0      | 0    | 1  | 1         |    | 6 7 |            | 12.875  | 15.45      | 20.6       | 15.45    | 19.3125 | 23.175  | 30.9    |

| 104 | 0  | 0         | 0  | 1  |       | 0      | 1    | 0  | 0         |    | 6 8 |            | 13      | 15.6       | 20.8       | 15.6     | 19.5    | 23.4    | 31.2    |

| 105 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 0  | 0         | 1  | 6 9 | 10.5       | 13.125  | 15.75      | 21         | 15.75    | 19.6875 | 23.625  | 31.5    |

| 106 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 0  | 1         | 0  | 6 A | 10.6       | 13.25   | 15.9       | 21.2       | 15.9     | 19.875  | 23.85   | 31.8    |

| 107 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 0  | 1         | 1  | 6 B | 10.7       | 13.375  | 16.05      | 21.4       | 16.05    | 20.0625 | 24.075  | 32.1    |

| 108 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 1  | 0         |    | 6 C | 10.8       | 13.5    | 16.2       | 21.6       | 16.2     | 20.25   | 24.3    | 32.4    |

| 109 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 1  | 0         |    | 6 D | 10.9       | 13.625  | 16.35      | 21.8       | 16.35    | 20.4375 | 24.525  | 32.7    |

| 110 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 1  | 1         | 0  | 6 E | 11         | 13.75   | 16.5       | 22         | 16.5     | 20.625  | 24.75   | 33      |

| 111 | 0  | 0         | 0  | 1  | 1     | 0      | 1    | 1  | 1         |    | 6 F | 11.1       | 13.875  | 16.65      | 22.2       | 16.65    | 20.8125 | 24.975  | 33.3    |

| 112 | 0  | 0         | 0  | 1  | 1     | 1      | 0    | 0  | 0         |    | 7 0 |            | 14      | 16.8       | 22.4       | 16.8     | 21      | 25.2    | 33.6    |

| 113 | 0  | 0         | 0  | 1  | 1     | 1      | 0    | 0  | 0         |    | 7 1 |            | 14.125  | 16.95      | 22.6       | 16.95    | 21.1875 | 25.425  | 33.9    |

| 114 | 0  | 0         | 0  | 1  | 1     | 1      | 0    | 0  | 1         |    | 7 2 |            | 14.25   | 17.1       | 22.8       | 17.1     | 21.375  | 25.65   | 34.2    |

| 115 | 0  | 0         | 0  | 1  | 1     | 1      | 0    | 0  | 1         |    | 7 3 |            | 14.375  | 17.25      | 23         | 17.25    | 21.5625 | 25.875  | 34.5    |

| 116 | 0  | 0         | 0  | 1  | 1     | 1      | 0    | 1  | 0         | 0  | 7 4 | 11.6       | 14.5    | 17.4       | 23.2       | 17.4     | 21.75   | 26.1    | 34.8    |

|     |           |           |    |    |           |           |       |    |           |    |     |            |         |            | Sam        | ple Rates | S       |         |         |

|-----|-----------|-----------|----|----|-----------|-----------|-------|----|-----------|----|-----|------------|---------|------------|------------|-----------|---------|---------|---------|

|     |           |           |    |    |           |           |       |    |           |    |     | 8.0<br>KHz | 6.4 KHz | 5.3<br>KHz | 4.0<br>KHz | 8.0 KHz   | 6.4 KHz | 5.3 KHz | 4.0 KHz |

|     |           |           |    |    |           |           |       |    |           |    |     |            |         |            | ISD Pa     | art Numb  | ers     |         |         |

|     |           |           |    |    |           |           |       |    |           |    |     | 1016A      | 1020A   |            |            |           |         |         |         |

|     |           |           |    |    |           |           |       |    |           |    |     | 1416       | 1420    |            |            |           |         |         |         |

|     |           |           |    | -  | Addre     | ess Ir    | nputs | 3  |           |    |     | 2532       | 2540    | 2548       | 2564       | 33060     | 33075   | 33090   | 33120-4 |

| DEC | <b>A9</b> | <b>A8</b> | Α7 | A6 | <b>A5</b> | <b>A4</b> | А3    | A2 | <b>A1</b> | Α0 |     | 2560       | 2575    | 2590       | 25120      | 33120     | 33150   | 33180   | 33240   |

| 117 | 0         | 0         | 0  | 1  | 1         | 1         | 0     | 1  | 0         | 1  | 7 5 | 11.7       | 14.625  | 17.55      | 23.4       | 17.55     | 21.9375 | 26.325  | 35.1    |

| 118 | 0         | 0         | 0  | 1  | 1         | 1         | 0     | 1  | 1         | 0  | 7 6 | 11.8       | 14.75   | 17.7       | 23.6       | 17.7      | 22.125  | 26.55   | 35.4    |

| 119 | 0         | 0         | 0  | 1  | 1         | 1         | 0     | 1  | 1         | 1  | 7 7 | 11.9       | 14.875  | 17.85      | 23.8       | 17.85     | 22.3125 | 26.775  | 35.7    |

| 120 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 0  | 0         | 0  | 7 8 | 12         | 15      | 18         | 24         | 18        | 22.5    | 27      | 36      |

| 121 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 0  | 0         | 1  | 7 9 | 12.1       | 15.125  | 18.15      | 24.2       | 18.15     | 22.6875 | 27.225  | 36.3    |

| 122 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 0  | 1         | 0  | 7 A | 12.2       | 15.25   | 18.3       | 24.4       | 18.3      | 22.875  | 27.45   | 36.6    |

| 123 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 0  | 1         | 1  | 7 B | 12.3       | 15.375  | 18.45      | 24.6       | 18.45     | 23.0625 | 27.675  | 36.9    |

| 124 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 1  | 0         | 0  | 7 C | 12.4       | 15.5    | 18.6       | 24.8       | 18.6      | 23.25   | 27.9    | 37.2    |

| 125 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 1  | 0         | 1  | 7 D | 12.5       | 15.625  | 18.75      | 25         | 18.75     | 23.4375 | 28.125  | 37.5    |

| 126 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 1  | 1         | 0  | 7 E | 12.6       | 15.75   | 18.9       | 25.2       | 18.9      | 23.625  | 28.35   | 37.8    |

| 127 | 0         | 0         | 0  | 1  | 1         | 1         | 1     | 1  | 1         | 1  | 7 F | 12.7       | 15.875  | 19.05      | 25.4       | 19.05     | 23.8125 | 28.575  | 38.1    |

| 128 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 0  | 0         | 0  | 8 0 | 12.8       | 16      | 19.2       | 25.6       | 19.2      | 24      | 28.8    | 38.4    |

| 129 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 0  | 0         | 1  | 8 1 | 12.9       | 16.125  | 19.35      | 25.8       | 19.35     | 24.1875 | 29.025  | 38.7    |

| 130 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 0  | 1         | 0  | 8 2 | 13         | 16.25   | 19.5       | 26         | 19.5      | 24.375  | 29.25   | 39      |

| 131 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 0  | 1         | 1  | 8 3 | 13.1       | 16.375  | 19.65      | 26.2       | 19.65     | 24.5625 | 29.475  | 39.3    |

| 132 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 1  | 0         | 0  | 8 4 | 13.2       | 16.5    | 19.8       | 26.4       | 19.8      | 24.75   | 29.7    | 39.6    |

| 133 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 1  | 0         | 1  | 8 5 | 13.3       | 16.625  | 19.95      | 26.6       | 19.95     | 24.9375 | 29.925  | 39.9    |

| 134 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 1  | 1         | 0  | 8 6 | 13.4       | 16.75   | 20.1       | 26.8       | 20.1      | 25.125  | 30.15   | 40.2    |

| 135 | 0         | 0         | 1  | 0  | 0         | 0         | 0     | 1  | 1         | 1  | 8 7 | 13.5       | 16.875  | 20.25      | 27         | 20.25     | 25.3125 | 30.375  | 40.5    |

| 136 | 0         | 0         | 1  | 0  | 0         | 0         | 1     | 0  | 0         | 0  |     | 13.6       | 17      | 20.4       | 27.2       | 20.4      | 25.5    | 30.6    | 40.8    |

| 137 | 0         | 0         | 1  | 0  | 0         | 0         | 1     | 0  | 0         | 1  | 8 9 | 13.7       | 17.125  | 20.55      | 27.4       | 20.55     | 25.6875 | 30.825  | 41.1    |

| 138 | 0         | 0         | 1  | 0  | 0         | 0         | 1     | 0  | 1         | 0  | 8 A | 13.8       | 17.25   | 20.7       | 27.6       | 20.7      | 25.875  | 31.05   | 41.4    |

| 139 | 0         | 0         | 1  | 0  | 0         | 0         | 1     | 0  | 1         | 1  | 8 B | 13.9       | 17.375  | 20.85      | 27.8       | 20.85     | 26.0625 | 31.275  | 41.7    |

| 140 | 0         | 0         |    | 0  |           | 0         |       | 1  | 0         |    | 8 C |            |         | 21         | 28         | 21        | 26.25   | 31.5    | 42      |

| 141 | 0         | 0         | 1  | 0  |           | 0         |       | 1  | 0         |    | 8 D |            | 17.625  | 21.15      | 28.2       | 21.15     | 26.4375 | 31.725  | 42.3    |

| 142 | 0         | 0         | 1  | 0  |           | 0         |       | 1  | 1         |    | 8 E | 14.2       | 17.75   | 21.3       | 28.4       | 21.3      | 26.625  | 31.95   | 42.6    |

| 143 | 0         | 0         | 1  | 0  | 0         | 0         |       | 1  | 1         |    | 8 F | 14.3       | 17.875  | 21.45      | 28.6       | 21.45     | 26.8125 | 32.175  | 42.9    |

| 144 | 0         | 0         | 1  | 0  |           | 1         | 0     | 0  | 0         |    | 9 0 |            | 18      | 21.6       | 28.8       | 21.6      | 27      | 32.4    | 43.2    |

| 145 | 0         | 0         | 1  | 0  |           | 1         | 0     | 0  | 0         |    | 9 1 | 14.5       | 18.125  | 21.75      | 29         | 21.75     | 27.1875 | 32.625  | 43.5    |

| 146 | 0         | 0         | 1  | 0  |           | 1         | 0     | 0  | 1         |    | 9 2 |            | 18.25   | 21.9       | 29.2       | 21.9      | 27.375  | 32.85   | 43.8    |

| 147 | 0         | 0         | 1  | 0  |           | 1         | 0     | 0  | 1         |    | 9 3 |            | 18.375  | 22.05      | 29.4       | 22.05     | 27.5625 | 33.075  | 44.1    |

| 148 | 0         | 0         | 1  | 0  | 0         | 1         | 0     | 1  | 0         |    | 9 4 |            | 18.5    | 22.2       | 29.6       | 22.2      | 27.75   | 33.3    | 44.4    |

| 149 | 0         | 0         | 1  | 0  |           | 1         | 0     | 1  | 0         |    | 9 5 |            | 18.625  | 22.35      | 29.8       | 22.35     | 27.9375 | 33.525  | 44.7    |

| 150 | 0         | 0         | 1  | 0  |           | 1         | 0     | 1  | 1         |    | 9 6 |            | 18.75   | 22.5       | 30         | 22.5      | 28.125  | 33.75   | 45      |

| 151 | 0         | 0         | 1  | 0  |           | 1         |       | 1  | 1         |    | 9 7 | 15.1       | 18.875  | 22.65      | 30.2       | 22.65     | 28.3125 | 33.975  | 45.3    |

| 152 | 0         | 0         | 1  | 0  |           | 1         | 1     | 0  | 0         |    | 9 8 |            | 19      | 22.8       | 30.4       | 22.8      | 28.5    | 34.2    | 45.6    |

| 153 | 0         | 0         | 1  | 0  | 0         | 1         | 1     | 0  | 0         | 1  | 9 9 | 15.3       | 19.125  | 22.95      | 30.6       | 22.95     | 28.6875 | 34.425  | 45.9    |

|     |    |           |      |      |       |        |       |      |           |       |     |            |          |            | Sam        | ple Rates | S         |         |         |

|-----|----|-----------|------|------|-------|--------|-------|------|-----------|-------|-----|------------|----------|------------|------------|-----------|-----------|---------|---------|

|     |    |           |      |      |       |        |       |      |           |       |     | 8.0<br>KHz | 6.4 KHz  | 5.3<br>KHz | 4.0<br>KHz | 8.0 KHz   | 6.4 KHz   | 5.3 KHz | 4.0 KHz |

|     |    |           |      |      |       |        |       |      |           |       |     |            |          |            | ISD Pa     | art Numbe | ers       |         |         |

|     |    |           |      |      |       |        |       |      |           |       |     | 1016A      | 1020A    |            |            |           |           |         |         |

|     |    |           |      |      |       |        |       |      |           |       |     | 1416       | 1420     |            |            |           |           |         |         |

|     |    |           |      | F    | Addre | ess Ir | nputs | 3    |           |       |     | 2532       | 2540     | 2548       | 2564       | 33060     | 33075     | 33090   | 33120-4 |

| DEC | Α9 | <b>A8</b> | Α7   | A6   | A5    | A4     | А3    | A2   | <b>A1</b> | A0    |     | 2560       | 2575     | 2590       | 25120      | 33120     | 33150     | 33180   | 33240   |

| 154 | 0  | 0         | 1    | 0    | 0     | 1      | 1     | 0    | 1         | 0     | 9 A | 15.4       | 19.25    | 23.1       | 30.8       | 23.1      | 28.875    | 34.65   | 46.2    |

| 155 | 0  | 0         | 1    | 0    | 0     | 1      | 1     | 0    | 1         | 1     | 9 B | 15.5       | 19.375   | 23.25      | 31         | 23.25     | 29.0625   | 34.875  | 46.5    |

| 156 | 0  | 0         | 1    | 0    | 0     | 1      | 1     | 1    | 0         | 0     | 9 ( | 15.6       | 19.5     | 23.4       | 31.2       | 23.4      | 29.25     | 35.1    | 46.8    |

| 157 | 0  | 0         | 1    | 0    | 0     | 1      | 1     | 1    | 0         | 1     | 9 D | 15.7       | 19.625   | 23.55      | 31.4       | 23.55     | 29.4375   | 35.325  | 47.1    |

| 158 | 0  | 0         | 1    | 0    | 0     | 1      | 1     | 1    | 1         | 0     | 9 E | 15.8       | 19.75    | 23.7       | 31.6       | 23.7      | 29.625    | 35.55   | 47.4    |

| 159 | 0  | 0         | 1    | 0    | 0     | 1      | 1     | 1    | 1         | 1     | 9 F | 15.9       | 19.875   | 23.85      | 31.8       | 23.85     | 29.8125   | 35.775  | 47.7    |

|     |    |           | "End | of M | lesso | age S  | Stora | ge S | pac       | e for | ISD | 1416, 18   | D1420, I | SD101      | 6A, and    | d ISD102  | 0A Device | s"      | •       |

|     |    |           |    |    |     |           |       |    |           |    |     |            |         |            | Sam        | ple Rates | 3       |         |         |

|-----|----|-----------|----|----|-----|-----------|-------|----|-----------|----|-----|------------|---------|------------|------------|-----------|---------|---------|---------|

|     |    |           |    |    |     |           |       |    |           |    |     | 8.0<br>KHz | 6.4 KHz | 5.3<br>KHz | 4.0<br>KHz | 8.0 KHz   | 6.4 KHz | 5.3 KHz | 4.0 KHz |

|     |    |           |    |    |     |           |       |    |           |    |     |            |         |            | ISD Pa     | rt Numbe  | ers     |         |         |

|     |    |           |    |    | Add | ress      | Input | s  |           |    |     | 2532       | 2540    | 2548       | 2564       | 33060     | 33075   | 33090   | 33120-4 |

| DEC | A9 | <b>A8</b> | A7 | A6 | A5  | <b>A4</b> | А3    | A2 | <b>A1</b> | A0 |     | 2560       | 2575    | 2590       | 25120      | 33120     | 33150   | 33180   | 33240   |

| 160 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 0  | 0         | 0  | A 0 | 16         | 20      | 24         | 32         | 24        | 30      | 36      | 48      |

| 161 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 0  | 0         | 1  | A 1 | 16.1       | 20.125  | 24.15      | 32.2       | 24.15     | 30.1875 | 36.225  | 48.3    |

| 162 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 0  | 1         | 0  | A 2 | 16.2       | 20.25   | 24.3       | 32.4       | 24.3      | 30.375  | 36.45   | 48.6    |

| 163 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 0  | 1         | 1  | A 3 | 16.3       | 20.375  | 24.45      | 32.6       | 24.45     | 30.5625 | 36.675  | 48.9    |

| 164 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 1  | 0         | 0  | A 4 | 16.4       | 20.5    | 24.6       | 32.8       | 24.6      | 30.75   | 36.9    | 49.2    |

| 165 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 1  | 0         | 1  | A 5 | 16.5       | 20.625  | 24.75      | 33         | 24.75     | 30.9375 | 37.125  | 49.5    |

| 166 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 1  | 1         | 0  | A 6 | 16.6       | 20.75   | 24.9       | 33.2       | 24.9      | 31.125  | 37.35   | 49.8    |

| 167 | 0  | 0         | 1  | 0  | 1   | 0         | 0     | 1  | 1         | 1  | A 7 | 16.7       | 20.875  | 25.05      | 33.4       | 25.05     | 31.3125 | 37.575  | 50.1    |

| 168 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 0  | 0         | 0  | A 8 | 16.8       | 21      | 25.2       | 33.6       | 25.2      | 31.5    | 37.8    | 50.4    |

| 169 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 0  | 0         | 1  | A 9 | 16.9       | 21.125  | 25.35      | 33.8       | 25.35     | 31.6875 | 38.025  | 50.7    |

| 170 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 0  | 1         | 0  | A A | 17         | 21.25   | 25.5       | 34         | 25.5      | 31.875  | 38.25   | 51      |

| 171 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 0  | 1         | 1  | A B | 17.1       | 21.375  | 25.65      | 34.2       | 25.65     | 32.0625 | 38.475  | 51.3    |

| 172 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 1  | 0         | 0  | A C | 17.2       | 21.5    | 25.8       | 34.4       | 25.8      | 32.25   | 38.7    | 51.6    |

| 173 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 1  | 0         | 1  | A D | 17.3       | 21.625  | 25.95      | 34.6       | 25.95     | 32.4375 | 38.925  | 51.9    |

| 174 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 1  | 1         | 0  | ΑE  | 17.4       | 21.75   | 26.1       | 34.8       | 26.1      | 32.625  | 39.15   | 52.2    |

| 175 | 0  | 0         | 1  | 0  | 1   | 0         | 1     | 1  | 1         | 1  | ΑF  | 17.5       | 21.875  | 26.25      | 35         | 26.25     | 32.8125 | 39.375  | 52.5    |

| 176 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 0  | 0         | 0  | ВО  | 17.6       | 22      | 26.4       | 35.2       | 26.4      | 33      | 39.6    | 52.8    |

| 177 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 0  | 0         | 1  | B 1 | 17.7       | 22.125  | 26.55      | 35.4       | 26.55     | 33.1875 | 39.825  | 53.1    |

| 178 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 0  | 1         | 0  | B 2 | 17.8       | 22.25   | 26.7       | 35.6       | 26.7      | 33.375  | 40.05   | 53.4    |

| 179 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 0  | 1         | 1  | В 3 | 17.9       | 22.375  | 26.85      | 35.8       | 26.85     | 33.5625 | 40.275  | 53.7    |

| 180 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 1  | 0         | 0  | B 4 | 18         | 22.5    | 27         | 36         | 27        | 33.75   | 40.5    | 54      |

| 181 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 1  | 0         | 1  | B 5 | 18.1       | 22.625  | 27.15      | 36.2       | 27.15     | 33.9375 | 40.725  | 54.3    |

|     |    |           |    |    |     |           |       |    |           |     |            |            |                 |            | Sam        | ple Rates     | 6                 |                 |              |

|-----|----|-----------|----|----|-----|-----------|-------|----|-----------|-----|------------|------------|-----------------|------------|------------|---------------|-------------------|-----------------|--------------|

|     |    |           |    |    |     |           |       |    |           |     |            | 8.0<br>KHz | 6.4 KHz         | 5.3<br>KHz | 4.0<br>KHz | 8.0 KHz       | 6.4 KHz           | 5.3 KHz         | 4.0 KHz      |

|     |    |           |    |    |     |           |       |    |           |     |            |            |                 |            | ISD Pa     | rt Numbe      | ers               |                 |              |

|     |    |           |    |    | Add | ress      | Input | ts |           |     |            | 2532       | 2540            | 2548       | 2564       | 33060         | 33075             | 33090           | 33120-4      |

| DEC | A9 | <b>A8</b> | A7 | A6 | A5  | <b>A4</b> | А3    | A2 | <b>A1</b> | A0  |            | 2560       | 2575            | 2590       | 25120      | 33120         | 33150             | 33180           | 33240        |

| 182 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 1  | 1         | 0   | В 6        | 18.2       | 22.75           | 27.3       | 36.4       | 27.3          | 34.125            | 40.95           | 54.6         |

| 183 | 0  | 0         | 1  | 0  | 1   | 1         | 0     | 1  | 1         | 1   | B 7        | 18.3       | 22.875          | 27.45      | 36.6       | 27.45         | 34.3125           | 41.175          | 54.9         |

| 184 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 0  | 0         | 0   | B 8        | 18.4       | 23              | 27.6       | 36.8       | 27.6          | 34.5              | 41.4            | 55.2         |

| 185 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 0  | 0         | 1   | В 9        | 18.5       | 23.125          | 27.75      | 37         | 27.75         | 34.6875           | 41.625          | 55.5         |

| 186 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 0  | 1         | 0   | ВА         | 18.6       | 23.25           | 27.9       | 37.2       | 27.9          | 34.875            | 41.85           | 55.8         |

| 187 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 0  | 1         | 1   | ВВ         | 18.7       | 23.375          | 28.05      | 37.4       | 28.05         | 35.0625           | 42.075          | 56.1         |

| 188 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 1  | 0         | 0   | ВC         | 18.8       | 23.5            | 28.2       | 37.6       | 28.2          | 35.25             | 42.3            | 56.4         |

| 189 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 1  | 0         | 1   | B D        | 18.9       | 23.625          | 28.35      | 37.8       | 28.35         | 35.4375           | 42.525          | 56.7         |

| 190 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 1  | 1         | 0   | ВЕ         | 19         | 23.75           | 28.5       | 38         | 28.5          | 35.625            | 42.75           | 57           |

| 191 | 0  | 0         | 1  | 0  | 1   | 1         | 1     | 1  | 1         | 1   | B F        | 19.1       | 23.875          | 28.65      | 38.2       | 28.65         | 35.8125           | 42.975          | 57.3         |

| 192 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 0  | 0         | 0   | C 0        | 19.2       | 24              | 28.8       | 38.4       | 28.8          | 36                | 43.2            | 57.6         |

| 193 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 0  | 0         | 1   | C 1        | 19.3       | 24.125          | 28.95      | 38.6       | 28.95         | 36.1875           | 43.425          | 57.9         |

| 194 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 0  | 1         | 0   | C 2        | 19.4       | 24.25           | 29.1       | 38.8       | 29.1          | 36.375            | 43.65           | 58.2         |

| 195 | 0  | 0         | 1  | 1  | 0   | 0         |       | 0  | 1         | 1   | C 3        | 19.5       | 24.375          | 29.25      | 39         | 29.25         | 36.5625           | 43.875          | 58.5         |

| 196 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 1  | 0         | 0   | C 4        | 19.6       | 24.5            | 29.4       | 39.2       | 29.4          | 36.75             | 44.1            | 58.8         |

| 197 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 1  | 0         | 1   | C 5        | 19.7       | 24.625          | 29.55      | 39.4       | 29.55         | 36.9375           | 44.325          | 59.1         |

| 198 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 1  | 1         | 0   | C 6        | 19.8       | 24.75           | 29.7       | 39.6       | 29.7          | 37.125            | 44.55           | 59.4         |

| 199 | 0  | 0         | 1  | 1  | 0   | 0         | 0     | 1  | 1         | 1   | C 7        | 19.9       | 24.875          | 29.85      | 39.8       | 29.85         | 37.3125           | 44.775          | 59.7         |

| 200 | 0  | 0         | 1  | 1  | 0   | 0         |       | 0  | 0         | 0   | C 8        | 20         | 25              | 30         | 40         | 30            | 37.5              | 45              | 60           |

| 201 | 0  | 0         | 1  | 1  | 0   | 0         | 1     | 0  | 0         | 1   | C 9        | 20.1       | 25.125          | 30.15      | 40.2       | 30.15         | 37.6875           | 45.225          | 60.3         |

| 202 | 0  | 0         | 1  | 1  | 0   | 0         | 1     | 0  | 1         | 0   | C A        | 20.2       | 25.25           | 30.3       | 40.4       | 30.3          | 37.875            | 45.45           | 60.6         |

| 203 | 0  | 0         | 1  | 1  | 0   | 0         | 1     | 0  | 1         |     | C B        | 20.3       | 25.375          | 30.45      | 40.6       | 30.45         | 38.0625           | 45.675          | 60.9         |

| 204 | 0  | 0         | 1  | 1  | 0   | 0         | 1     | 1  | 0         | 0   | СС         | 20.4       | 25.5            | 30.6       | 40.8       | 30.6          | 38.25             | 45.9            | 61.2         |

| 205 | 0  | 0         | 1  | 1  | 0   | 0         |       | 1  | 0         | 1   | C D        | 20.5       | 25.625          | 30.75      | 41         | 30.75         | 38.4375           | 46.125          | 61.5         |

| 206 | 0  | 0         | 1  | 1  | 0   | 0         | 1     | 1  | 1         | 0   | C E        | 20.6       | 25.75           | 30.9       | 41.2       | 30.9          | 38.625            | 46.35           | 61.8         |

| 207 | 0  | 0         | 1  |    | 0   | 0         |       | 1  | 1         | - 1 | C F        |            | 25.875          |            |            |               | 38.8125           | 46.575          |              |

| 208 | 0  | 0         | 1  | 1  | 0   |           |       | 0  | 0         | 0   | D 0        |            | 26              | 31.2       | 41.6       | 31.2          | 39                | 46.8            | 62.4         |

| 209 | 0  | 0         | 1  | 1  | 0   | ]         | 0     | 0  | 0         |     | D 1        | 20.9       | 26.125          |            | 41.8       | 31.35         | 39.1875           | 47.025          | 62.7         |

| 210 | 0  | 0         | 1  | 1  | 0   |           | 0     | 0  | 1         | 0   | D 2        | 21         | 26.25           | 31.5       | 42         | 31.5          | 39.375            | 47.25           | 63           |

| 211 | 0  | 0         | 1  | 1  | 0   | 1         | 0     | 0  | 1         | 1   | D 3        | 21.1       | 26.375          |            | 42.2       | 31.65         | 39.5625           | 47.475          | 63.3         |

| 212 | 0  | 0         | 1  | 1  | 0   | 1         | 0     | 1  | 0         | 0   | D 4        | 21.2       | 26.5            | 31.8       | 42.4       | 31.8          | 39.75             | 47.7            | 63.6         |

| 213 | 0  | 0         | 1  | 1  | 0   | 1         | 0     |    | 0         | 1   | D 5        | 21.3       | 26.625          |            | 42.6       | 31.95         | 39.9375           | 47.925          | 63.9         |

| 214 | 0  | 0         | 1  | 1  | 0   | 1         | 0     | 1  | 1         | 0   | D 6        | 21.4       | 26.75           | 32.1       | 42.8       | 32.1          | 40.125            | 48.15           | 64.2         |

| 215 | 0  |           |    | 1  |     |           |       | 0  | 1         | 1   | D 7        | 21.5       | 26.875          |            | 43         | 32.25         | 40.3125           | 48.375          | 64.5         |