El número de la revista QEX de

mayo/junio de 2008 incluye un interesantísimo artículo de

James Ahlstrom, N2ADR, titulado (traducción) “Un excitador de

SSB enteramente digital para HF”. Se trata de un transmisor de

300 milivatios en SSB y CW para todas las bandas de aficionado

de HF, cuyos componentes no son los que se verían en el

interior de un equipo QRP convencional, sino unos pocos

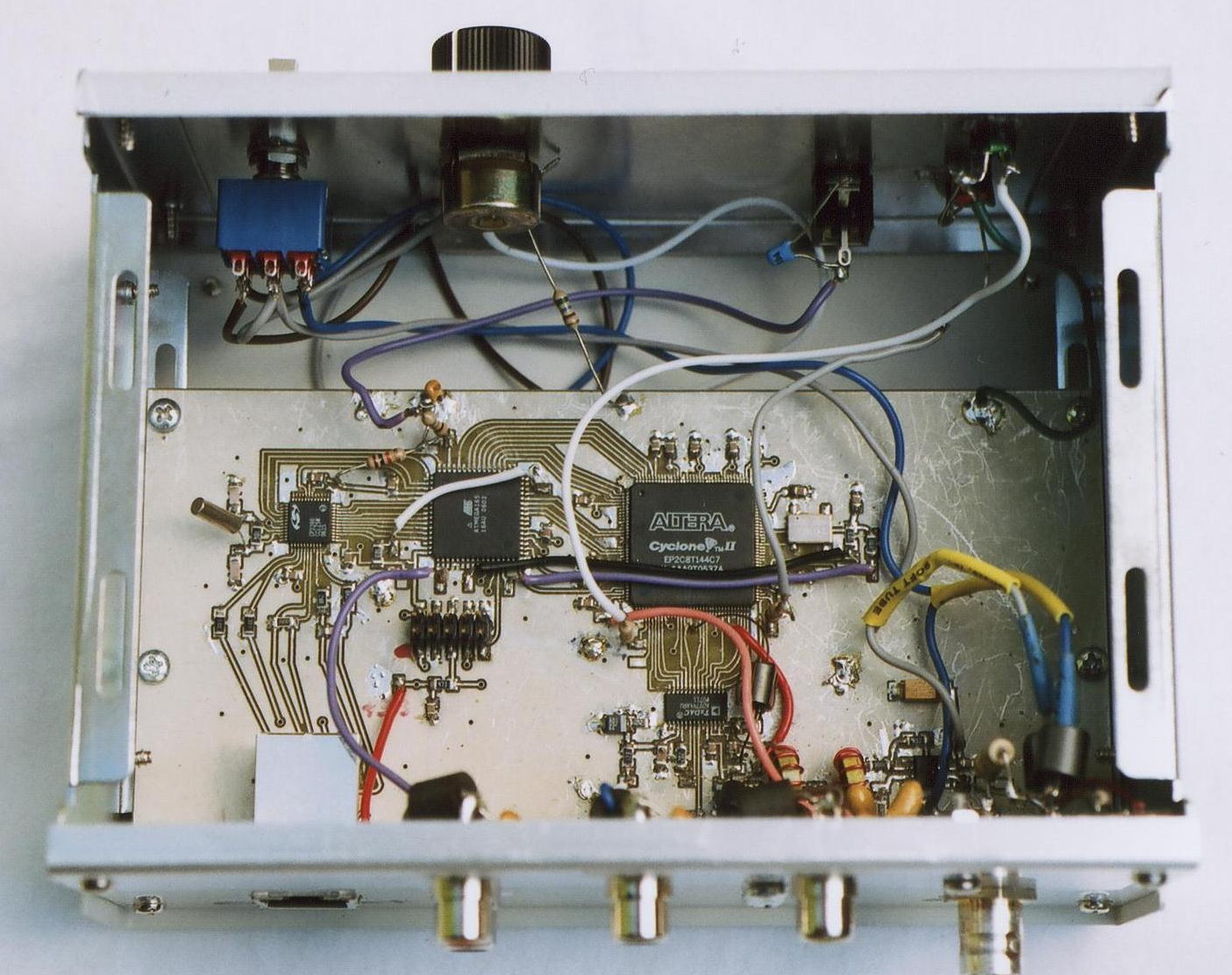

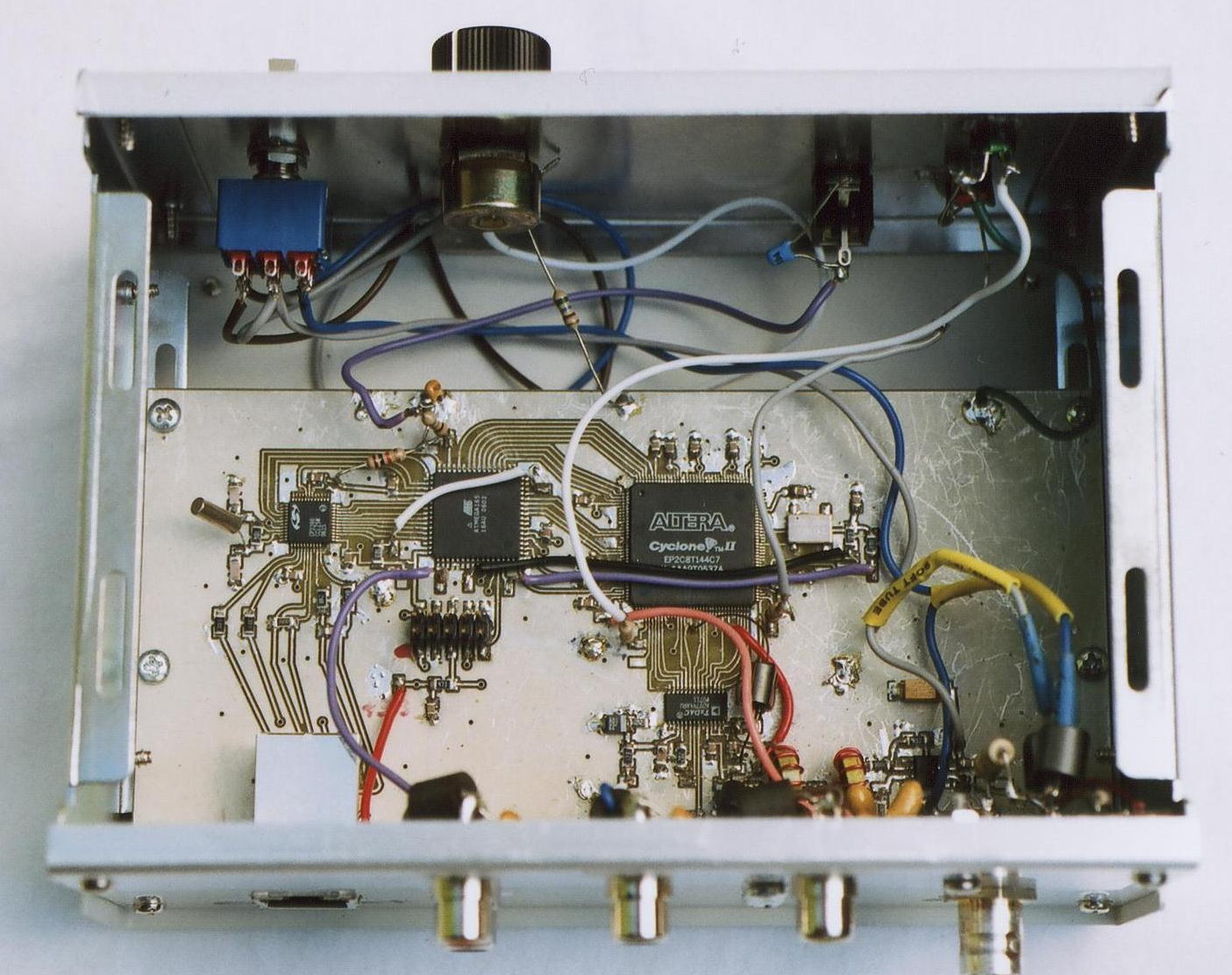

circuitos integrados (ver foto A); ello es debido a que es un

diseño en el que el proceso de generación de señal y

modulación (SSB) es llevado a cabo digitalmente.

El núcleo del transmisor es un dispositivo FPGA: un “chip” FPGA (Field Programmable Gate Array) tiene decenas de pines de entrada o salida, y está compuesto por miles de pequeños bloques o celdas, programables para llevar a cabo sencillas funciones de lógica digital; asimismo, las conexiones entre dichas celdas son también sujetas a programación. Por tanto, un FPGA puede realizar diferentes funciones más o menos complejas, en función de cómo sea programado.

La programación de un FPGA no se realiza como si se tratase de un procesador u ordenador, es decir, con una serie de instrucciones a ejecutar una tras otra, sino mediante un lenguaje de descripción de circuitos que detalla el conexionado entre los distintos bloques que forman el FPGA y las funciones de cada uno, o bien la funcionalidad total del circuito buscado. Así, podemos imaginar un FPGA como un circuito en el que se ejecutan varios procesos simultáneamente (en ocasiones, todos).

Foto A. Transmisor QRP para SSB y CW en las bandas de HF, realizado en torno a un circuito FPGA (a la derecha de la placa de circuito impreso). Foto cortesía de James Ahlstrom, N2ADR

Los lenguajes de programación de FPGA más conocidos son VHDL y Verilog, y los dos principales productores de estos dispositivos son Xilinx y Altera. Existen dispositivos FPGA reconfigurables, mientras que otros son programables una sola vez. Muchos equipos de telecomunicaciones y electrónicos en general basan su funcionamiento en un FPGA, y su capacidad de actualización a nuevas versiones en la carga de un nuevo programa para el FPGA; es el caso de equipos de radio definidos por software (SDR) como el receptor Perseus y algunas placas del proyecto HPSDR, en cuyos núcleos se halla también un FPGA.

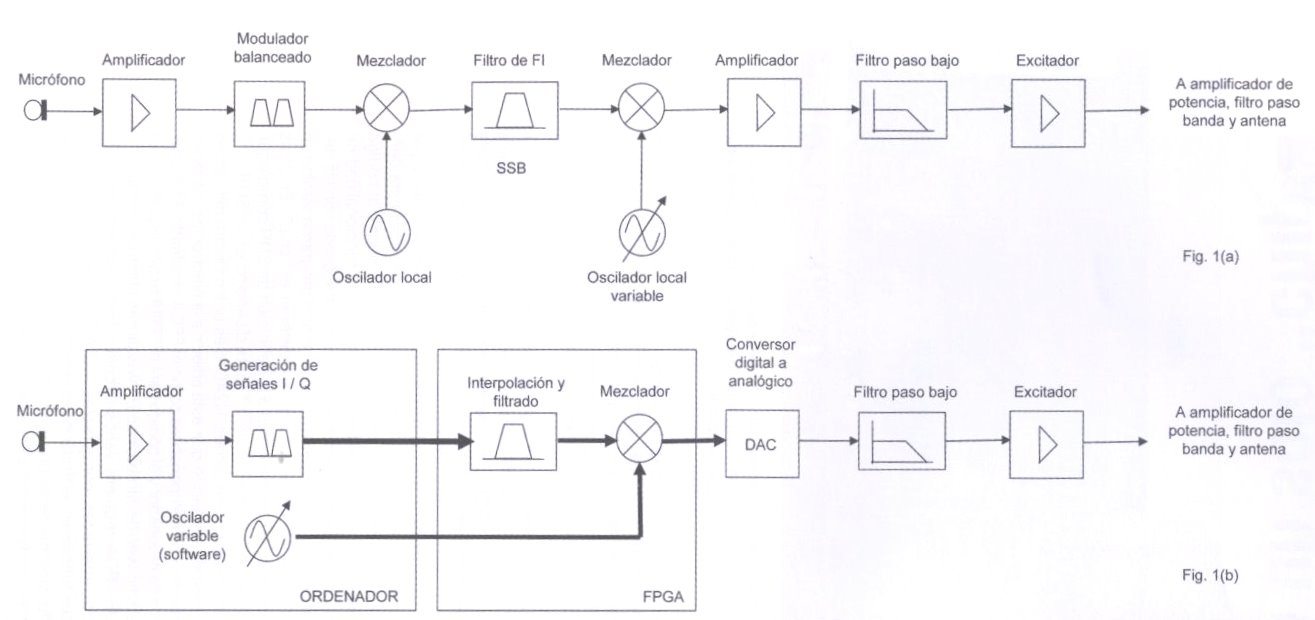

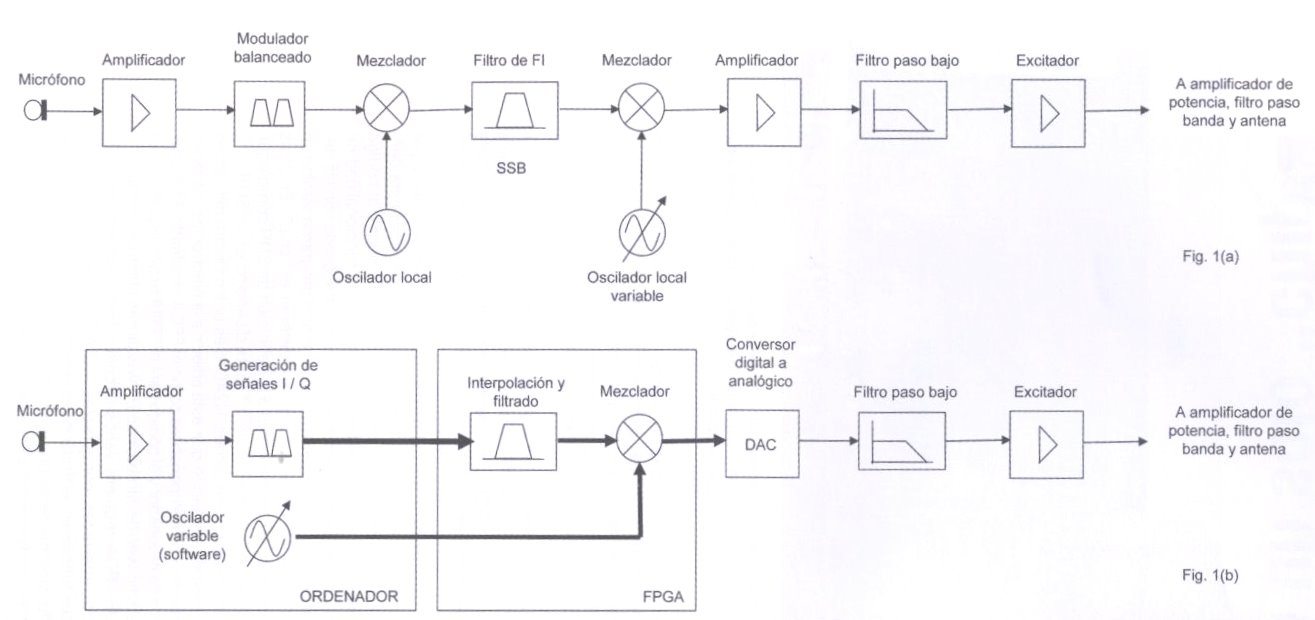

En la figura 1(b) se observa el diagrama de bloques del diseño de James. En primer lugar, una tarjeta de sonido externa conectada a un puerto USB de un ordenador tipo PC funcionando bajo Linux; el micrófono para SSB está conectado a dicha tarjeta, y un programa escrito por el propio James (fácilmente transportable a Windows) recoge las muestras de voz y las convierte en las señales en fase y cuadratura (I y Q), para entregarlas digitalizadas al transmisor mediante una conexión Ethernet. El programa para CW es otro, y no es difícil imaginar software para otros modos, como RTTY y PSK31.

Figura 1. (a): ejemplo de diagrama de bloques de un transmisor de banda lateral única (SSB); (b): diagrama de bloques del transmisor comentado en el texto

Una vez en el FPGA, las señales I/Q, cuya velocidad es de 48.000 muestras por segundo, son interpoladas para subir su velocidad a 90 millones de muestras por segundo, y ser filtradas y multiplicadas digitalmente por otra señal de misma velocidad de muestreo y de una frecuencia que será la de emisión. Esta etapa tendría su “equivalente” analógico en un mezclador convencional, con la diferencia de que aquí el proceso es realizado numéricamente, en el interior del FPGA. En cuanto al filtro, su misión es eliminar las señales “imagen” inherentes al muestreo de las señales I/Q.

La frecuencia de dicha señal es generada en el ordenador mediante un algoritmo llamado CORDIC, de uso habitual en equipos SDR, que permite generar señales sinusoidales fácilmente y empleando poca potencia de cálculo, y sin el gasto de memoria que supone tener almacenado el rango de valores de un ciclo de sinusoidal; este algoritmo realiza la función que llevaría a cabo un oscilador en un equipo “convencional”.

Llegados a este punto, ya tenemos la señal a emitir pero en formato digital: el FPGA la entrega a un conversor digital a analógico (DAC), que creará una señal analógica apta para ser entregada a un filtro paso bajo, etapas amplificadoras, filtro paso banda y finalmente, antena.

¿Puede decirse que es un equipo SDR? Depende de lo que entendamos por tal: por un lado su funcionalidad está definida por software (el programa en el ordenador y el código Verilog del FPGA), pero por otra parte esa funcionalidad no puede ser cambiada sobre la marcha de acuerdo con las necesidades, ya que exige la carga de otro programa Verilog en el FPGA, proceso que requiere detener el “chip”. En otras palabras: si nos atenemos a la definición de SDR como equipo reconfigurable “al vuelo”, este diseño no es un SDR.

Este prototipo de James, N2ADR, es una muestra del campo de experimentación que está abierto a la electrónica y la radioafición, con componentes como el FPGA empleado. El programa de ordenador y el código para el FPGA están disponibles en el sitio web de James, http://www.james.ahlstrom.name.

Un FPGA requiere varios circuitos complementarios (control, interfaces, conversores A/D ó D/A) para poder realizar sus funciones; el titular de este artículo no significa lo contrario, solamente se pretende resaltar que en el diseño de James, las funciones principales las lleva a cabo el FPGA.

Página de inicio

El núcleo del transmisor es un dispositivo FPGA: un “chip” FPGA (Field Programmable Gate Array) tiene decenas de pines de entrada o salida, y está compuesto por miles de pequeños bloques o celdas, programables para llevar a cabo sencillas funciones de lógica digital; asimismo, las conexiones entre dichas celdas son también sujetas a programación. Por tanto, un FPGA puede realizar diferentes funciones más o menos complejas, en función de cómo sea programado.

La programación de un FPGA no se realiza como si se tratase de un procesador u ordenador, es decir, con una serie de instrucciones a ejecutar una tras otra, sino mediante un lenguaje de descripción de circuitos que detalla el conexionado entre los distintos bloques que forman el FPGA y las funciones de cada uno, o bien la funcionalidad total del circuito buscado. Así, podemos imaginar un FPGA como un circuito en el que se ejecutan varios procesos simultáneamente (en ocasiones, todos).

Foto A. Transmisor QRP para SSB y CW en las bandas de HF, realizado en torno a un circuito FPGA (a la derecha de la placa de circuito impreso). Foto cortesía de James Ahlstrom, N2ADR

Los lenguajes de programación de FPGA más conocidos son VHDL y Verilog, y los dos principales productores de estos dispositivos son Xilinx y Altera. Existen dispositivos FPGA reconfigurables, mientras que otros son programables una sola vez. Muchos equipos de telecomunicaciones y electrónicos en general basan su funcionamiento en un FPGA, y su capacidad de actualización a nuevas versiones en la carga de un nuevo programa para el FPGA; es el caso de equipos de radio definidos por software (SDR) como el receptor Perseus y algunas placas del proyecto HPSDR, en cuyos núcleos se halla también un FPGA.

En la figura 1(b) se observa el diagrama de bloques del diseño de James. En primer lugar, una tarjeta de sonido externa conectada a un puerto USB de un ordenador tipo PC funcionando bajo Linux; el micrófono para SSB está conectado a dicha tarjeta, y un programa escrito por el propio James (fácilmente transportable a Windows) recoge las muestras de voz y las convierte en las señales en fase y cuadratura (I y Q), para entregarlas digitalizadas al transmisor mediante una conexión Ethernet. El programa para CW es otro, y no es difícil imaginar software para otros modos, como RTTY y PSK31.

Figura 1. (a): ejemplo de diagrama de bloques de un transmisor de banda lateral única (SSB); (b): diagrama de bloques del transmisor comentado en el texto

Una vez en el FPGA, las señales I/Q, cuya velocidad es de 48.000 muestras por segundo, son interpoladas para subir su velocidad a 90 millones de muestras por segundo, y ser filtradas y multiplicadas digitalmente por otra señal de misma velocidad de muestreo y de una frecuencia que será la de emisión. Esta etapa tendría su “equivalente” analógico en un mezclador convencional, con la diferencia de que aquí el proceso es realizado numéricamente, en el interior del FPGA. En cuanto al filtro, su misión es eliminar las señales “imagen” inherentes al muestreo de las señales I/Q.

La frecuencia de dicha señal es generada en el ordenador mediante un algoritmo llamado CORDIC, de uso habitual en equipos SDR, que permite generar señales sinusoidales fácilmente y empleando poca potencia de cálculo, y sin el gasto de memoria que supone tener almacenado el rango de valores de un ciclo de sinusoidal; este algoritmo realiza la función que llevaría a cabo un oscilador en un equipo “convencional”.

Llegados a este punto, ya tenemos la señal a emitir pero en formato digital: el FPGA la entrega a un conversor digital a analógico (DAC), que creará una señal analógica apta para ser entregada a un filtro paso bajo, etapas amplificadoras, filtro paso banda y finalmente, antena.

¿Puede decirse que es un equipo SDR? Depende de lo que entendamos por tal: por un lado su funcionalidad está definida por software (el programa en el ordenador y el código Verilog del FPGA), pero por otra parte esa funcionalidad no puede ser cambiada sobre la marcha de acuerdo con las necesidades, ya que exige la carga de otro programa Verilog en el FPGA, proceso que requiere detener el “chip”. En otras palabras: si nos atenemos a la definición de SDR como equipo reconfigurable “al vuelo”, este diseño no es un SDR.

Este prototipo de James, N2ADR, es una muestra del campo de experimentación que está abierto a la electrónica y la radioafición, con componentes como el FPGA empleado. El programa de ordenador y el código para el FPGA están disponibles en el sitio web de James, http://www.james.ahlstrom.name.

Un FPGA requiere varios circuitos complementarios (control, interfaces, conversores A/D ó D/A) para poder realizar sus funciones; el titular de este artículo no significa lo contrario, solamente se pretende resaltar que en el diseño de James, las funciones principales las lleva a cabo el FPGA.

Página de inicio