# AMBE-2000™ Vocoder Chip User's Manual

Version 4.0 January 2003

# AMBE-2000™ Vocoder Chip User's Manual

Version 4.0 January, 2003 Copyright ©, 2003 Digital Voice Systems, Inc 234 Littleton Road Westford, MA 01886

This document may not, in whole or in part be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form without prior consent in writing from Digital Voice Systems, Incorporated. Every effort has been made to ensure the accuracy of this manual. However, Digital Voice Systems, Inc. makes no warranties with respect to the documentation and disclaims any implied warranties of merchantability and fitness for a particular purpose. Digital Voice Systems, Inc. shall not be liable for any errors or for incidental or consequential damages in connection with the furnishing, performance, or use of this manual or the examples herein. This includes business interruption and/or other loss which may arise from the use of this product. The information in this document is subject to change without notice.

### **Trademarks**

AMBE-2000<sup>TM</sup> Vocoder Chip is a registered trademark of Digital Voice Systems, Inc. Other product names mentioned may be trademarks or registered trademarks of their respective companies and are the sole property of their respective manufacturers. All Rights Reserved

Data subject to change

# AMBE-2000<sup>™</sup> Vocoder Chip END USER License Agreement

#### 1.0 Preliminary Statements and Definitions

- $1.1~{\rm "END~USER"}$  shall mean the person and/or organization to whom the AMBE-2000  ${\rm ^{TM}}$  Vocoder Chip was delivered or provided to as specified in the purchase order or other documentation. In the event that the END USER transfers his rights under this license to a third party as specified in section 2.2, then this third party shall become an "END USER".

- 1.2 Digital Voice Systems, Inc. (DVSI) has developed a voice coding method and algorithm (the "Technology") based on the Advanced Multi-Band Excitation ("AMBE®") voice coder. The technology codes speech at bit rates of 2.4 to 9.6 kilobits per second (kbps) including error correction bits

- correction bits.

1.3 "AMBE® Voice Compression Software" shall mean the speech coding software and/or firmware integrated into the AMBE-2000™ Vocoder chip integrated circuit.

- 1.4 "Voice Codec" shall mean the AMBE-2000<sup>TM</sup> Vocoder Chip integrated circuit, the AMBE® Voice Compression Software, firmware and associated documentation, including modifications, enhancements and extensions made by or for Digital Voice Systems, Inc. (DVSI) and including circuit diagrams, timing diagrams, logic diagrams, layouts, operating instructions and user manuals

- 1.5 DVSI represents that it owns certain "Proprietary Rights" in the Technology and the AMBE® Voice Compression Software, including patent rights in the Technology, and patent rights, copyrights, and trade secrets in the AMBE® Voice Compression Software.

#### 2.0 License Granted

- 2.1 Subject to the conditions herein and upon initial use of the AMBE-2000™ Vocoder Chip, DVSI hereby grants to END USER a non-exclusive, limited license to use the AMBE\* Voice Compression Software in machine readable form solely on the AMBE-2000™ Vocoder Chip. Title to the AMBE\* Voice Compression Software remains with DVSI. No license is granted for use of the AMBE\* Voice Compression Software on other than the AMBE-2000™ Vocoder Chip. No license, right or interest in any trademark, trade name or service mark of DVSI is granted under this Agreement.

- Static duract mass Agreement.

2.2 END USER shall not copy, extract, de-compile, reverse engineer or disassemble the AMBE® Voice Compression Software contained in the AMBE-2000™ Vocoder Chip.

#### 3.0 Transfer of License

3.1 The END USER shall have the right to transfer the AMBE-2000™ Vocoder Chip and all rights under this Agreement to a third party by either (i) providing the third party with a copy of this Agreement or (ii) providing the third party with an agreement written by the END USER (hereinafter "END USER Agreement") so long as the END USER Agreement is approved in writing by DVSI prior to transfer of the AMBE-2000™ Vocoder Chip. The END USER Agreement shall contain comparable provisions to those contained herein for protecting the Proprietary Information from disclosure by such third party. Third parties shall agree to accept all the terms and conditions under either Agreement or the END USER Agreement.

#### 4.0 Term and Termination

- 4.1 This Agreement is effective upon initial delivery of the Voice Codec and shall remain in effect until terminated in accordance with this agreement.

4.2 This Agreement shall terminate automatically without notice from DVSI if END USER fails

- 4.2 This Agreement shall terminate automatically without notice from DVSI if END USER fails to comply with any of the material terms and conditions herein. END USER may terminate this Agreement at any time upon written notice to DVSI certifying that END USER has complied with the provisions of Section 3.3.

- 4.3 Upon termination of this Agreement for any reason, END USER shall: (i) return all AMBE-2000<sup>TM</sup> Vocoder Chip purchased or acquired, or in Licensee's possession, to DVSI; (ii) have no further rights to any AMBE<sup>®</sup> Voice Compression Software or the Technology without a separate written license from DVSI; (iii) discontinue all use of the AMBE-2000<sup>TM</sup> Vocoder Chip;

#### 5.0 Payments

5.1 In consideration of the materials provided as part of the Voice Codec, and in consideration of the license and rights in the AMBE® Voice Compression Software granted by DVSI, and in consideration of DVSI's performance of its obligations hereunder, END USER agrees to pay to DVSI the fee specified in DVSI's invoice.

#### 6.0 Proprietary Notices

6.1 END USER shall not remove any copyright or proprietary notice on the AMBE-2000<sup>TM</sup> Vocoder Chip or on the AMBE $^{\odot}$  Voice Compression Software.

#### 7.0 Proprietary Information

- 7.1 The parties agree that the AMBE® Voice Compression Software shall be considered Proprietary Information

- 7.2 Except as otherwise provided in this Agreement, END USER shall not use, disclose, make, or have made any copies of the Proprietary Information, in whole or in part, without the prior written consent of DVSI.

#### 8.0 Limited Warranty

- 8.1 DVSI warrants the Voice Codec to be free from defects in materials and workmanship under normal use for a period of ninety (90) days from the date of delivery.

8.2 Except as stated in Section 7.1, the Voice Codec is provided "as is" without warranty of any kind. DVSI does not warrant, guarantee or make any representations regarding the use, or the results of the use, of the Voice Codec with respect to its correctness, accuracy, reliability, correctness or otherwise. The entire risk as to the results and performance of the Voice Codec is assumed by the END USER. After expiration of the warranty period, END USER, and not DVSI or its employees, assumes the entire cost of any servicing, repair, replacement, or corrections of the Voice Codec.

- correction of the Voice Codec.

8.3 DVSI represents that, to the best of its knowledge, it has the right to enter into this Agreement and to grant a license to use the AMBE® Voice Compression Software to END USER

- 8.4 Except as specifically set forth in this Section 7.0, DVSI makes no express or implied warranties including, without limitation, the warranties of merchantability or fitness for a particular purpose or arising from a course of dealing, usage or trade practice, with respect to the Voice Codec. Some states do not allow the exclusion of implied warranties, so the above exclusion may not apply to END USER. No oral or written information or advice given by DVSI or its employees shall create a warranty or in any way increase the scope of this warranty, and END USER may not rely on any such information or advice. The limited warranties under this section 7.0 give END USER specific legal rights, and END USER may have other rights which vary from state to state.

#### 9.0 Limitation of Liability

9.1 In no event shall DVSI be liable for any special, incidental, indirect or consequential damages resulting from the use or performance of the Voice Codec whether based on an action in contract, tort (including negligence) or otherwise (including, without limitation, damages for loss of business profits, business interruption, and loss of business information), even if DVSI or any DVSI representative has been advised of the possibility of such damages.

9.2 Because some states do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitations may not apply to END USER.

9.3 DVSI's maximum liability for damages arising under this Agreement shall be limited to 20% (twenty percent) of the fees paid by END USER for the particular Voice Codec which caused the damages or that is the subject matter of, or is directly related to, the cause of action.

#### 10.0 Taxes

10.1 All payments required under Section 4.0 or otherwise under this Agreement are exclusive of taxes and END USER agrees to bear and be responsible for the payment of all such taxes (except for taxes based upon DVSI's income) including, but not limited to, all sales, use, rental receipt, personal property or other taxes which may be levied or assessed in connection with this Agreement.

#### 11.0 Export

11.1 United States export laws and regulations prohibit the exportation of certain products or technical data received from DVSI under this Agreement to certain countries except under a special validated license. As of November 30, 1999 the restricted countries are: Libya, Cuba, North Korea, Iraq, Serbia, Taliban in Afghanistan, Sudan, Burma, Yugoslavia and Iran. The END USER hereby gives its assurance to DVSI that it will not knowingly, unless prior authorization is obtained from the appropriate U.S. export authority, export or re-export, directly or indirectly to any of the restricted countries any products or technical data received from DVSI under this Agreement in violation of said United States Export Laws and Regulations. DVSI neither represents that a license is not required nor that, if required, it will be issued by the U.S. Department of Commerce. Licensee shall assume complete and sole responsibility for obtaining any licenses required for export purposes.

#### 12.0 Governing Law

12.1 This Agreement is made under and shall be governed by and construed in accordance with the laws of the Commonwealth of Massachusetts, except that body of law governing conflicts of law. If any provision of this Agreement shall be held unenforceable by a court of competent jurisdiction, that provision shall be enforced to the maximum extent permissible, and the remaining provisions of this Agreement shall remain in full force and effect.

| 1. Prod                                                   | uct Introduction                                                                                                        | 6                                      |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.1                                                       | General Information                                                                                                     | 6                                      |

| 1.2                                                       | Advantages                                                                                                              | 6                                      |

| 1.3                                                       | Typical Applications                                                                                                    | 7                                      |

| 2. AMB                                                    | E-2000™ Application Design Overview                                                                                     | 8                                      |

| 2.1                                                       | Basic Operation                                                                                                         | 8                                      |

| 2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                   | Channel Interface Overview                                                                                              | 8<br>8<br>9<br>10<br>11                |

| 3 Hard                                                    | ware Information                                                                                                        | 12                                     |

| 3.1<br>3.1.1                                              | Special Handling Instructions Storage                                                                                   | 12<br>12                               |

| 3.2                                                       | Pin Descriptions                                                                                                        | 13                                     |

| 3.3                                                       | Clock and Reset Timing                                                                                                  | 15                                     |

| 3.4                                                       | Associated Chip Delay                                                                                                   | 17                                     |

| 3.5<br>3.5.1<br>3.5.2                                     | Crystal / Oscillator Usage TTL Clock Source Crystal Oscillator                                                          | <i>17</i><br>17<br>18                  |

| 3.6                                                       | Package Description                                                                                                     | 19                                     |

| 3.7                                                       | Normal Operating Conditions                                                                                             | 20                                     |

| 3.8                                                       | Absolute Maximum Ratings                                                                                                | 20                                     |

| 3.9                                                       | Electrical Characteristics and Requirements                                                                             | 20                                     |

| 4 Chan                                                    | nel Interface                                                                                                           | 21                                     |

| 4.1                                                       | Overview                                                                                                                | 21                                     |

| 4.2                                                       | Serial Configuration Selection                                                                                          | 22                                     |

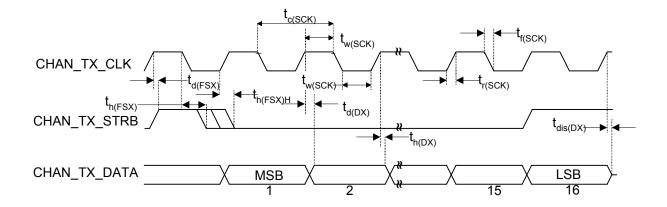

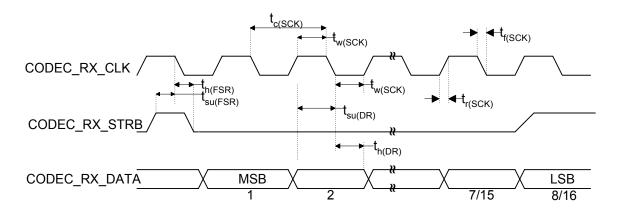

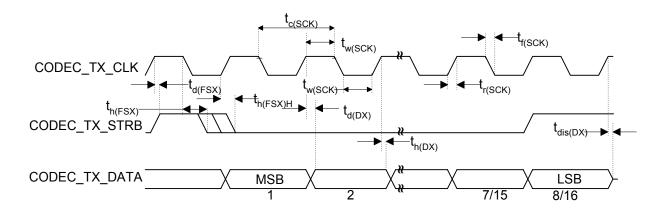

| <i>4.3</i><br>4.3.1                                       | Channel Serial Mode Low Level Timing for Passive and Active Serial Mode                                                 | 23<br>24                               |

| 5 Chan                                                    | nel Data Format                                                                                                         | 26                                     |

| 5.1                                                       | Framed Format                                                                                                           | 26                                     |

| 5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6 | Framed Input: Word 1 : Control Word 1 Framed Input: Words 2-6 : Rate Information Framed Input: Word 7 : Unused in Input | 26<br>27<br>27<br>27<br>27<br>28<br>28 |

| <b>DVSI Confide</b><br>Visit us at <u>www</u>             | ential Proprietary, Subject to Change<br>advsinc.com                                                                    | Page 4                                 |

| 5.<br>5.<br>5.                                             | .2.7 Framed Input: Word 9 : Unused in Input .2.8 Framed Input: Word 10 : DTMF Control .2.9 Framed Input: Word 11 : Control Word 2 .2.10 30 .2.11 Framed Input: Words 12-23 : Channel Data                                                                                                                                                                                                                                                                                                                               | 29<br>29<br>29<br>30                                                 |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 5.<br>5.<br>5.<br>5.<br>5.<br>5.                           | Framed Output  3.1 Framed Output: Word 0 : Header  3.2 Framed Output: Word 1 : Power Control ID  3.3 Framed Output: Word 1 : Control Word 1  3.4 Framed Output: Words 2-6 : Rate Information  3.5 Framed Output: Word 7 : Bit Error Rate  3.6 Framed Output: Word 8 : Soft Decision Distance  3.7 Framed Output: Word 9 : Detected Bit Errors  3.8 Framed Output: Word 10 : DTMF Control  3.9 Framed Output: Word 11 : Control Word 2  3.10 Framed Output: Words 12-23 : Channel Data                                   | 31<br>31<br>31<br>32<br>32<br>32<br>32<br>33<br>34<br>35             |

|                                                            | Unframed Serial Format  .4.1 Unframed Serial Output Format  .4.2 Unframed Serial Input Format                                                                                                                                                                                                                                                                                                                                                                                                                           | 35<br>35<br>36                                                       |

| 6 A                                                        | /D-D-A Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                   |

| 6.1                                                        | A/D-D/A Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                   |

|                                                            | Configuring the A/D-D/A Interface using CODEC_SEL [1-0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                   |

| 6.2                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| 6.2<br>6.3                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38                                                                   |

| 6.3                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38<br><b>40</b>                                                      |

| 6.3                                                        | Low Level A/D–D/A Timing  Special Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| 6.3<br><b>7 S</b>                                          | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                   |

| 6.3<br><b>7 S</b><br>7.1                                   | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection                                                                                                                                                                                                                                                                                                                                                                                                                | <b>40</b>                                                            |

| 6.3 <b>7 S</b> 7.1  7.2                                    | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection  Echo Cancellation                                                                                                                                                                                                                                                                                                                                                                                             | <b>40</b><br>40<br>40                                                |

| 6.3 <b>7 S</b> 7.1  7.2  7.3                               | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection  Echo Cancellation  Voice Activation Detection (VAD), Comfort Noise Insertion (CNI)                                                                                                                                                                                                                                                                                                                            | <b>40</b><br>40<br>40<br>41                                          |

| 6.3  7 S  7.1  7.2  7.3  7.4  7.5  7.6  7.                 | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection  Echo Cancellation  Voice Activation Detection (VAD), Comfort Noise Insertion (CNI)  Dual Tone Multiple Frequency, Detection and Generation                                                                                                                                                                                                                                                                    | <b>40</b> 40 40 41 42                                                |

| 6.3  7 S  7.1  7.2  7.3  7.4  7.5  7.6  7.                 | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection  Echo Cancellation  Voice Activation Detection (VAD), Comfort Noise Insertion (CNI)  Dual Tone Multiple Frequency, Detection and Generation  Normal Power and Power Saving Modes  6.1 Standard Sleep Mode  6.2 Power Down                                                                                                                                                                                      | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>42<br>42                   |

| 6.3  7 S  7.1  7.2  7.3  7.4  7.5  7.6  7.7  7.7           | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection  Echo Cancellation  Voice Activation Detection (VAD), Comfort Noise Insertion (CNI)  Dual Tone Multiple Frequency, Detection and Generation  Normal Power and Power Saving Modes  6.1 Standard Sleep Mode  6.2 Power Down                                                                                                                                                                                      | 40<br>40<br>41<br>42<br>42<br>42<br>43                               |

| 6.3  7 S  7.1  7.2  7.3  7.4  7.5  7.6  7.7  7.7           | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note Coding Rate Selection Echo Cancellation Voice Activation Detection (VAD), Comfort Noise Insertion (CNI) Dual Tone Multiple Frequency, Detection and Generation Normal Power and Power Saving Modes 6.1 Standard Sleep Mode 6.2 Power Down Slip Enable                                                                                                                                                                                 | 40<br>40<br>41<br>42<br>42<br>42<br>42<br>43<br>44                   |

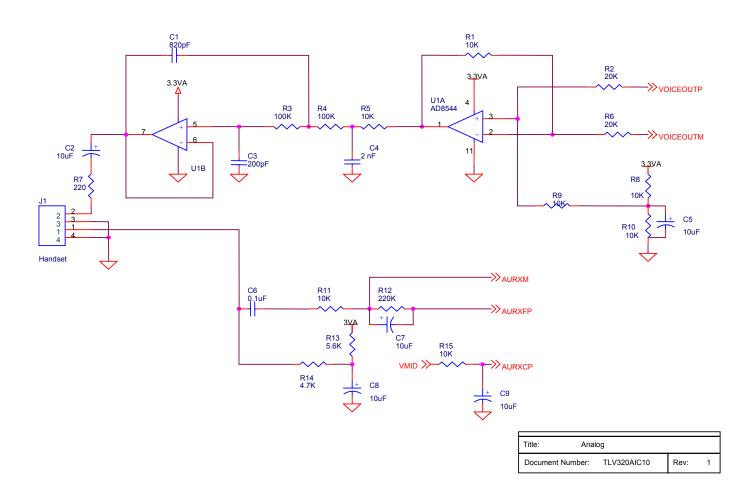

| 6.3  7 S  7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.7                  | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note  Coding Rate Selection  Echo Cancellation  Voice Activation Detection (VAD), Comfort Noise Insertion (CNI)  Dual Tone Multiple Frequency, Detection and Generation  Normal Power and Power Saving Modes  6.1 Standard Sleep Mode  6.2 Power Down  Slip Enable  Appendices  Example A/D-D/A Usage                                                                                                                                      | 40<br>40<br>41<br>42<br>42<br>42<br>43<br>44<br>48                   |

| 6.3  7 S  7.1  7.2  7.3  7.4  7.5  7.6  7.7  7.7  8 A  8.1 | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note Coding Rate Selection Echo Cancellation Voice Activation Detection (VAD), Comfort Noise Insertion (CNI) Dual Tone Multiple Frequency, Detection and Generation Normal Power and Power Saving Modes 6.1 Standard Sleep Mode 6.2 Power Down Slip Enable  Appendices  Example A/D-D/A Usage Example: Texas Instruments TLV320AIC10 Usage                                                                                                 | 40<br>40<br>41<br>42<br>42<br>42<br>43<br>44<br>48                   |

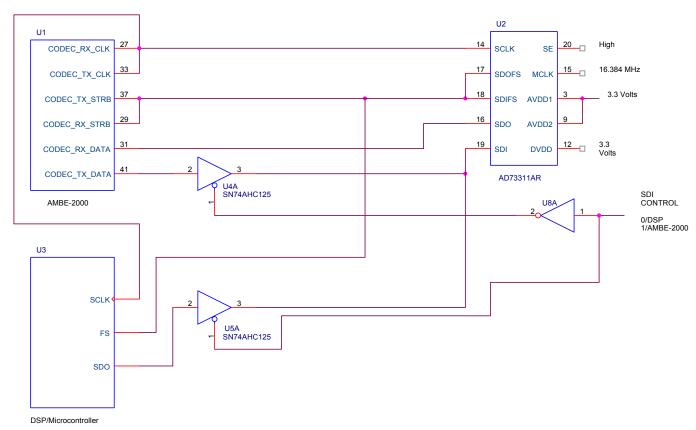

| 6.3 7 S  7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.7 8 A 8.1 8.2       | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note Coding Rate Selection Echo Cancellation Voice Activation Detection (VAD), Comfort Noise Insertion (CNI) Dual Tone Multiple Frequency, Detection and Generation Normal Power and Power Saving Modes 6.1 Standard Sleep Mode 6.2 Power Down Slip Enable  Appendices  Example A/D-D/A Usage Example: Texas Instruments TLV320AIC10 Usage Configuring the AD73311 for 3-Volt Operation                                                    | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>43<br>44<br>48<br>48       |

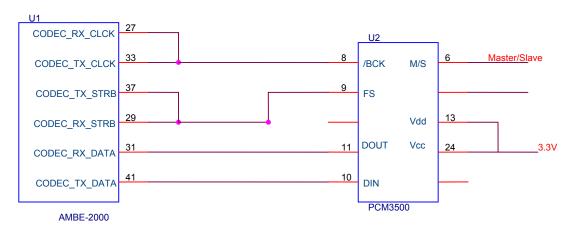

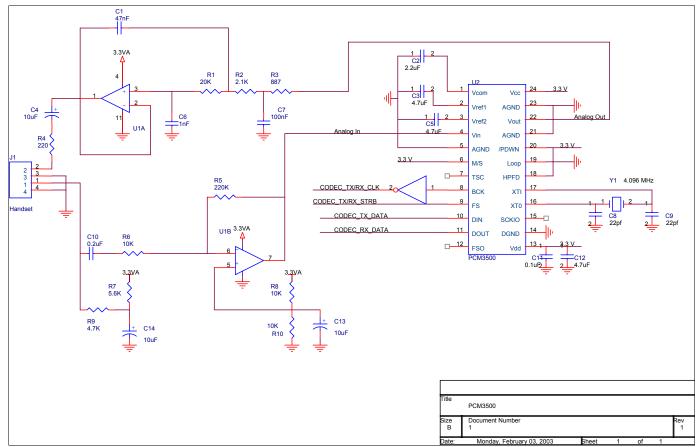

| 6.3  7 S  7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.7  8 A 8.1 8.2 8.3 | Low Level A/D–D/A Timing  Special Functions  Hardware vs. Software Selection Note Coding Rate Selection Echo Cancellation Voice Activation Detection (VAD), Comfort Noise Insertion (CNI) Dual Tone Multiple Frequency, Detection and Generation Normal Power and Power Saving Modes 6.1 Standard Sleep Mode 6.2 Power Down Slip Enable  Appendices  Example A/D-D/A Usage Example: Texas Instruments TLV320AIC10 Usage Configuring the AD73311 for 3-Volt Operation Interfacing to the Texas Instruments PCM3500 Codec | 40<br>40<br>41<br>42<br>42<br>42<br>43<br>44<br>48<br>48<br>49<br>54 |

### 1. Product Introduction

### 1.1 General Information

Digital Voice Systems Inc.'s AMBE-2000<sup>TM</sup> Vocoder Chip is an extremely flexible, high-performance, single chip, speech compression coder. It provides superior voice quality at low data rates. It provides a real-time, full-duplex implementation of the standard-setting AMBE® voice compression software algorithm. DVSI's patented AMBE® voice compression technology has been proven to outperform CELP, RELP, VSELP, MELP, ECELP, MP-MLQ, LPC-10, and other competitive technologies. Numerous evaluations have shown its ability to provide performance equal to today's digital cellular systems at under half the data rate. The AMBE® voice compression algorithm is used in applications throughout the world, including the next generation of digital mobile communication systems.

The AMBE-2000<sup>TM</sup> Vocoder chip provides a high degree of flexibility in selecting the speech and FEC (Forward Error Correction) data rates. The user can separately select these parameters in 50 bps increments for total rates from 2.0 kbps to 9.6 kbps. Typically for higher error rate channels, the user will apportion a greater percentage of the total bit rate to FEC coding. The AMBE-2000<sup>TM</sup> voice coder maintains natural voice quality and speech intelligibility at rates as low as 2.0 kbits/sec. The AMBE® algorithm's low complexity allows it to be fully integrated into a low cost, low power integrated circuit, the AMBE-2000<sup>TM</sup> Vocoder Chip.

The AMBE-2000<sup>TM</sup> Vocoder Chip offers similar features to DVSI's AMBE-1000<sup>TM</sup> Vocoder Chip allowing it to be incorporated into systems already designed for the AMBE-1000<sup>TM</sup> and is interoperable with other DVSI products. The AMBE-2000<sup>TM</sup> Vocoder Chip delivers improved performance and enhanced modes such as 4.0 kbps toll quality speech and convolutional FEC coding. Along with these enhancements the AMBE-2000<sup>TM</sup> Vocoder Chip employs a control interface along with the variable data rates and FEC selection.

# 1.2 Advantages

- Superior Voice Quality

- Low Cost

- No External Memory Required

- · Robust to Bit Errors & Background Noise

- Variable Data Rates 2.0 kbps to 9.6 kbps

- Variable FEC Rates 50 bps to 7.2 kbps

- Very Low Power (65mW @ 3.3V, 0.11mW Deep Sleep)

- Compact Single Chip Solution: 100 pin TQFP

#### **Features**

- High Quality Low Data Rate Speech Coding

- DVSI's Full Duplex AMBE® Voice Coder

- Supports Data Rates of 2.0 kbps to 9.6 kbps in 50 bps increments

- User Selectable Forward Error Correction rates

- Viterbi Decoder (rate 1/4 or more)

- 16 Level Soft Decision Decoding

- Voice Activity Detection (VAD) / Comfort Noise Insertion

- 16 ms Echo Cancellation

- Single and Dual Tone (DTMF) Detection and Generation

- Power-Down Mode

Page 6

- Minimal algorithmic processing delay

- DTMF detection and regeneration with North American call progress tones

# 1.3 Typical Applications

- Satellite Communications

- Digital Mobile Radio

- Secure Communications

- · Cellular Telephony and PCS

- Voice Multiplexing

- Voice Mail

- Multimedia Applications

# 2. AMBE-2000™ Application Design Overview

# 2.1 Basic Operation

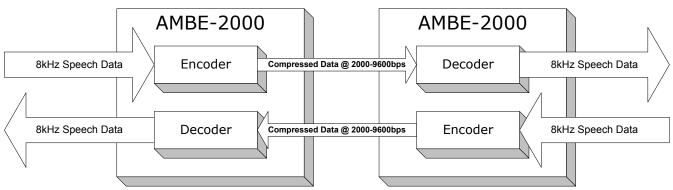

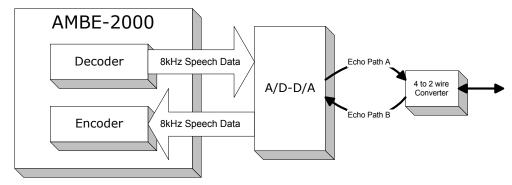

In its simplest model, the AMBE-2000<sup>TM</sup> can be viewed as two separate components, the **Encoder** and the **Decoder**. The Encoder receives an 8kHz sampled stream of *speech* data (16-bit linear, 8-bit Alaw, or 8-bit ulaw) and outputs a stream of *channel* data at the desired rate. Conversely the Decoder receives a stream of *channel* data and synthesizes a stream of *speech* data. The timing for the interfaces for the AMBE-2000<sup>TM</sup> Encoder and Decoder are fully asynchronous.

Figure 2 - A. Basic Operation

Typically the speech interface is an external A/D-D/A chip. The format of the incoming and outgoing speech data streams are coupled, that is to say they must be the same format (16-bit linear, 8-bit Alaw, or 8-bit  $\mu$ law). The channel interface is commonly (but not limited to) an 8 or 16 bit microprocessor or other suitable 'glue logic' hardware capable of performing the rudimentary formatting functions between the AMBE-2000<sup>TM</sup> channel format and the format of the system channel under design.

Optional functions of the chip, such as echo cancellation, voice activation/detection, power mode control, data/FEC rate selection, etc. are controlled either through hardware control pins (see Section 5) and/or through the decoder command interface (see Section 4) Data sent into the decoder for function control purposes is distinguished from the data to be decoded into speech through a channel format which is described in Section 4.

# 2.2 Initial Design Considerations

Some of the initial design considerations the application engineer will face are the following:

- Choice of A/D-D/A chip.

- Choice of Channel Interface.

- Speech and FEC Rates.

# 2.2.1 A/D – D/A Overview

The choice of the A/D-D/A chip is critical to designing a system with superior voice quality. Given that Alaw and µlaw companding chips are already incorporating some compression to reduce the number of bits per sample, it is recommended that, when possible, a 16-bit linear device be used for maximum voice quality. When choosing a device, pay particular attention to Signal to Noise ratios and Frequency Responses of any filters that may be present on the analog front end of these chips. The Alaw and µlaw interfaces are also provided for the design engineer who is trying to fit to pre-existing conditions or is under other cost type restraints.

Downloaded from **Elcodis.com** electronic components distributor

### 2.2.2 Vocoder Front End Requirements

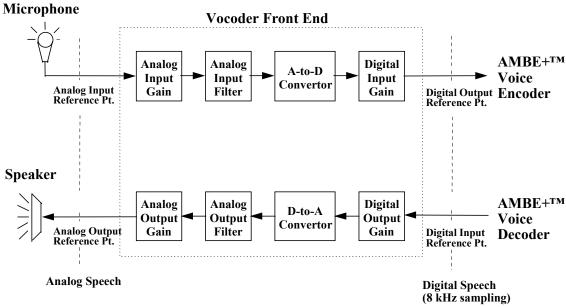

In order to ensure proper performance from the voice coder, it is necessary for the vocoder front end to meet a set of minimum performance requirements. For the purposes of this section the vocoder front end is considered to be the total combined response between microphone/speaker and the digital PCM interface to the vocoder, as shown in Figure 2-B. This includes any analog electronics plus the A-to-D and D-to-A converters as well as any digital filtering performed prior to the voice encoder or after the voice decoder.

Figure 2 - B. Vocoder Front End

The AMBE+TM voice encoder and decoder operate with unity (i.e. 0 dB) gain. Consequently the analog input and output gain elements shown in Figure 2 are only used to match the sensitivity of the microphone and speaker with the A-to-D converters and D-to-A converters, respectively. It is recommended that the analog input gain be set such that the RMS speech level under nominal input conditions is 25 dB below the saturation point of the A-to-D converter (+3 dBm0). This level, which equates to -22 dBm0, is designed to provide sufficient margin to prevent the peaks of the speech waveform from being clipped by the A-to-D converter.

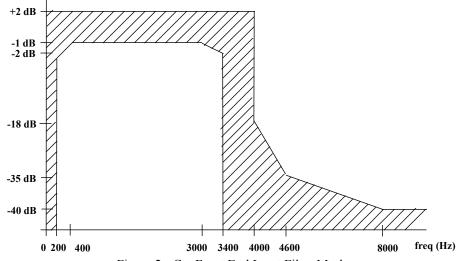

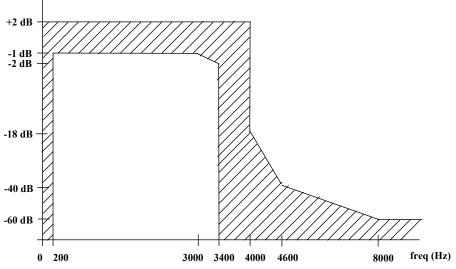

Figure 2 - C. Front End Input Filter Mask

The voice coder interface requires the A-to-D and D-to-A converters to operate at an 8 kHz sampling rate (i.e. a sampling period of 125 microseconds) at the digital input/output reference points. This requirement necessitates the use of analog filters at both the input and output to eliminate any frequency components above the Nyquist frequency (4 kHz). The recommended input filter mask is shown in Figure 2 - C, and the recommended output filter mask is shown in Figure 2 - D. For proper operation, the shaded zone of the respective figure should bound the frequency response of the front-end input and output.

Figure 2 - D. Front End Output Filter Mask

This document assumes that the A-to-D converter produces digital samples where the maximum digital input level (+3 dBm0) is defined to be +/- 32767, and similarly, that the maximum digital output level of the D-to-A converter occurs at the same digital level of +/- 32767. If a converter is used which does not meet these assumptions then the digital gain elements shown in Figure 2 should be adjusted appropriately. Note that these assumptions are automatically satisfied if 16 bit linear A-to-D and D-to-A converters are used, in which case the digital gain elements should be set to unity gain.

An additional recommendation addresses the maximum noise level measured at the output reference points shown in Figure 2-B with the corresponding inputs set to zero. DVSI recommends that the noise level for both directions should not exceed -60 dBm0 with no corresponding input. In addition the isolation from cross talk (or echo) from the output to the input should exceed 45 dB which can be achieved via either passive (electrical and/or acoustic design) or active (echo cancellation and/or suppression) means.

#### 2.2.3 Channel Interface Overview

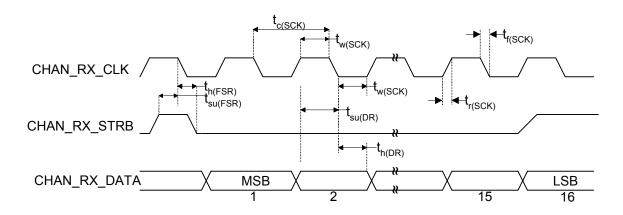

The channel interface is meant to be flexible to allow for easy integration with the system under design. The basic hardware unit of the interface is a serial port. The serial port can run in *passive* or *active* modes. In passive mode, all of the channel interface control signals are inputs to the AMBE-2000<sup>TM</sup> chip. In active mode, only the TX\_DATA\_STRB is an output from the AMBE-2000<sup>TM</sup> chip. All other signals are inputs.

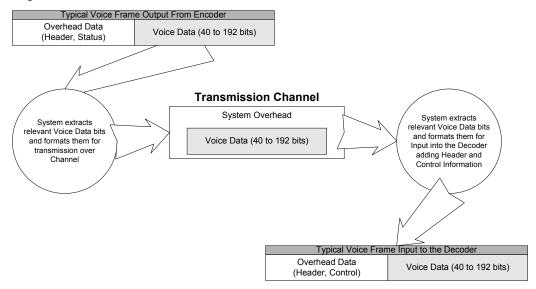

Under normal operation, every 20ms, the encoder outputs a frame of coded bits, and the decoder needs to be delivered a frame of coded bits. There is some formatting of the data for both the encoder and the decoder. The primary purpose of the formatting is to provide alignment information for the encoded bit stream. The data has two formats, *Framed* and *Unframed*. Serial mode can run in either **Framed** *or* **Unframed** mode.

The **Framed** and **UnFramed Modes** are explained in full detail in Section 4, but essentially the two formats are trying to achieve the same function, to provide positional information regarding the outgoing and incoming coded data streams. In **Framed** mode each 20ms of output data from the encoder is preceded by a known structure (each packet corresponds to 20 ms of speech data input to the encoder). This structure also embeds some status type flags, meant for local control purposes, within it. The only data from the **Framed** format that is typically sent across the transmission channel under design are the actual encoded bits at the desired rate.

In **Framed** mode, it is the responsibility of the designed system to pass enough information along with the encoded bits such that the **Framed** format needed by the decoder can be reconstructed on the other side. This extra information, or overhead, is going to be very specific to the system under design, but at a minimum needs to pass enough information to reliably reconstruct the 20msec frame structure at the other end for the decoder.

In **Unframed** mode the data coming out of the encoder can be thought of as a continuous stream of voice data with the framing information embedded within the encoded bits. One advantage of this type of set-up is that the system does not have to add any bandwidth for overhead to the channel. The disadvantage is that the decoder needs 10-12 incoming frames in order to gain synchronization with the data stream before it can properly synthesize the speech waveform. The **Unframed** mode only commits a single bit per frame to maintain data alignment. In higher error rate channels the performance will be improved by adding more bits per frame to the alignment information (which is more easily performed when using **Framed** mode).

Additional flexibility is given to the channel interface to the encoder and decoder by allowing the AMBE-2000<sup>TM</sup> Vocoder Chip to run in *Passive* or *Active* modes. In Passive mode, data strobes are provided by an external source, while in Active mode, data strobes are provided by the AMBE-2000<sup>TM</sup> Vocoder Chip. The serial interfaces can be run in Passive or Active modes. See Section 4 for full details and timing for both **Framed** and **Unframed** data.

#### 2.2.4 Speech and FEC Rate Selection Overview

The total coded bit rate is the sum of two components, the Speech Data bit rate and the Forward Error Correction (FEC) Data bit rate. The addition of FEC data to the speech data allows the decoder to be able to correct a limited amount of errors within each frame should they arrive corrupted. If the channel is expected to have more errors then more bits should be dedicated to FEC. At the same time, voice quality will increase if the number of speech bits is increased.

# 3 Hardware Information

# 3.1 Special Handling Instructions

The AMBE-2000<sup>TM</sup> uses the TM320LC541B-66 core. For more details on handling, electrical characteristics, packaging, or timing constraints please refer to the TMS320-C54x manual found at <a href="http://www-s.ti.com/sc/psheets/sprs039c/sprs039c.pdf">http://www-s.ti.com/sc/psheets/sprs039c/sprs039c.pdf</a> (Adobe Acrobat). Although the AMBE-2000<sup>TM</sup> Vocoder Chip incorporates input protection circuitry, to avoid damage from the accumulation of a static charge, industry standard electrostatic discharge precautions and procedures must be employed during handling and mounting.

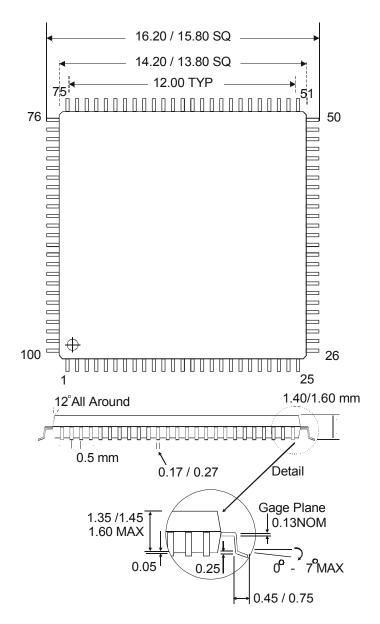

The 100 pin TQFP package design of the AMBE-2000<sup>TM</sup> Vocoder Chip allows it to be mounted by infrared reflow, vaporphase reflow or equivalent processes. The peak package body temperature must not exceed 220°C. The AMBE-2000<sup>TM</sup> Vocoder Chip requires baking before mounting, if any of the following conditions exist:

- Humidity indicator card (included in packaging) shows exposure to > 20 % when read at 23°C + 5°C

- Devices were not shipped in a package designated as "moisture controlled."

- Not mounted within 168 hours of receipt, at factory conditions of ≤30°C and <60% RH

- If the device has not been stored at ≤ 20% RH

DVSI's recommended bake out procedures:

- For low-temperature device containers: 192 hours at 40°C + 5°C / -0°C and < 5% Relative Humidity

- For high-temperature device containers: 24 hours at 125°C + 5°C.

# 3.1.1 Storage

To insure maximum shelf life in long term storage, AMBE-2000<sup>™</sup> Vocoder Chips should be kept in a moisture controlled package at <40°C and <90% Relative Humidity

# 3.2 Pin Descriptions

| The CHAN_SEL1 Input Channel Interface Selection Pins: Use these bits to select the channel interface type (framed, unframed, active and passive) according to Table 4-A. See full description in section 4.2.  The CHAN_SEL0 Input CODEC_SEL1 Input CODEC_SEL1 Input CODEC_SEL0 Input  | Pin Number | Pin Descriptive Name | Pin Direction | Notes                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|---------------|-----------------------------------------------------------------------------------------|

| A/D-D/A Select Pins see Table 6-A to select the interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77         | CHAN_SEL1            | Input         | (framed, unframed, active and passive) according to Table 4-A. See full description in  |

| AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface.  AD-D/A Select Pins see Table 6-A to select the interface and see the interface and seed in the control word interface and seed in the control word interface and seed searched in section 5.2.4.  AD-D/A Select Pins see Table 6-A to select the interface and seed in the control word interface and seed in the control word interface and seed searched in section 5.2.4.  AD-D/A Select Pins see Table Pin. Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as described in section 5.2.9.  BECHOCAN_EN Input Select Pins. Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as described in section 5.2.9.  BECHOCAN_EN Input Select Pins. Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as described in section 5.2.9.  BECHOCAN_EN Input Select Pins Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as describe | 75         | CHAN_SEL0            | Input         | Used with CHAN_SEL1 to select channel operation mode                                    |

| RATE_SEL4 Input  73 RATE_SEL2 Input  74 RATE_SEL2 Input  75 RATE_SEL2 Input  76 RATE_SEL1 Input  77 RATE_SEL1 Input  78 RATE_SEL1 Input  88 VAD_EN Input  89 VAD_EN Input  80 VAD_EN Input  80 SLEEP_EN Input  81 SLEEP_EN Input  82 SLIP_EN Input  84 SLYCIKIN Input  85 SCICKIN Input  86 SAZCIKIN Input  87 AND SINCE SECTION INPUT  88 SALEEP_EN Input  89 SOFT_EN Input  80 RESETN Input  80 RESETN Input  81 BAUD_SEL1 Input  82 CHAN_RX_DATA Input  84 CHAN_RX_CLK Input  85 CABAN_RX_STRB Input  86 CHAN_RX_STRB Input  87 CODEC_TX_STRB Input  88 FAME SELO CABING RATE SELO Output Frame synchronization pulse for D/A data. Should be connected to CODEC_TX_STRB  89 CODEC_TX_STRB Input  80 FALSERS SELO CODEC_RX_STRB Input  80 CODEC_TX_STRB Input  80 CODEC_TX_STRB Input  80 CODEC_TX_STRB Input  80 CODEC_TX_STRB Input  81 Fame synchronization pulse for D/A data. Should be connected to CODEC_TX_STRB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85         | CODEC_SEL1           | Input         |                                                                                         |

| RATE_SEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84         | CODEC_SEL0           | Input         | A/D-D/A Select Pins see Table 6-A to select the interface.                              |

| RATE_SEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74         | RATE_SEL4            | Input         |                                                                                         |

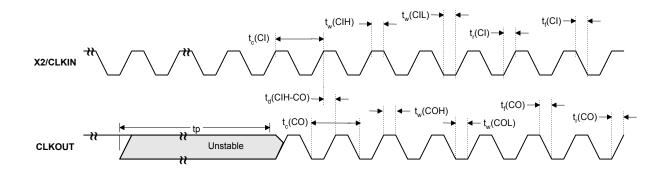

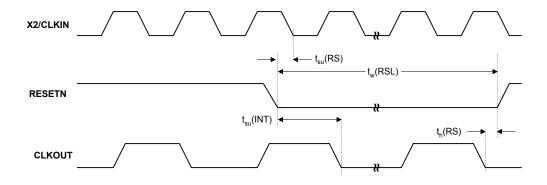

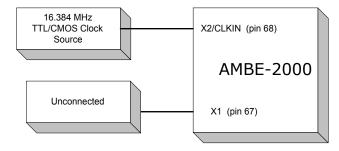

| 72       RATE_SEL2       Input       section 7.2. The coding rates are also selectable using the Control Word interface described in section 5.2.4.         71       RATE_SEL1       Input       described in section 5.2.4.         70       RATE_SEL0       Input       Voice Activation Detection Enable Pin. Active HIGH. See Section 7.4. VAD can also be enabled/disabled using the Control Word interface as described in section 5.2.9.         78       ECHOCAN_EN       Input       Echo Canceller Enable Pin. Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as described in section 5.2.9.         83       SLEEP_EN       Input       Standard Sleep Enable Pin. Active HIGH. See Section 7.6.1.         82       SLIP_EN       Input       Slip Control Enable Pin. Active HIGH. See Section 7.7.         68       X2/CLKIN       Input       Clock Input 1. 16.384 Mbz input. See Section 3.3         67       X1       Input       AMBE-2000™ Reset pin. Active LOW. See Section 3.3         69       RESETN       Input       AMBE-2000™ Reset pin. Active LOW. See Section 3.3         20       EPR       Output       Encode Packet Ready: Following a reset, this signal will have a high to low transition to indicate the first packet is ready. The next packet will be ready approximately 20 msee later. See Note 1.         79       SOFT_EN       Input       Soft decision decoding enable. Enables 4 bit soft decisi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73         | RATE_SEL3            | Input         | Coding Pata Salact Pine: Use these hits to salact the voice and EEC rates according to  |

| 71 RATE_SEL1 Input 70 RATE_SEL0 Input 70 RATE_SEL0 Input 70 RATE_SEL0 Input 86 VAD_EN Input Voice Activation Detection Enable Pin. Active HIGH. See Section 7.4. VAD can also be enabled/disabled using the Control Word interface as described in section 5.2.9.  78 ECHOCAN_EN Input Echo Canceller Enable Pin. Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as described in section 5.2.9.  83 SLEEP_EN Input Standard Sleep Enable Pin. Active HIGH. See Section 7.6.1.  82 SLIP_EN Input Slip Control Enable Pin. Active HIGH. See Section 7.7.  68 X2/CLKIN Input Clock Input 1. 16.384 Mhz input. See Section 3.3  67 X1 Input Output from internal oscillator for the crystal. If the internal oscillator is not used this pin should be unconnected.  69 RESETN Input AMBE-2000™ Reset pin. Active LOW. See Section 3.3  20 EPR Output Encode Packet Ready: Following a reset, this signal will have a high to low transition to indicate the first packet is ready. The next packet will be ready approximately 20 msee later. See Note 1.  80 BAUD_SEL0 Input Soft decision decoding enable. Enables 4 bit soft decision error decoder.  81 BAUD_SEL1 Input Channel Receive Data to AMBE-2000™  42 CHAN_RX_DATA Input Channel Receive Data to AMBE-2000™  43 CHAN_RX_CLK Input Channel Transmit Data from AMBE-2000™  44 CHAN_TX_STRB I/O Channel Transmit Data Strobe  45 CHAN_RX_STRB Input Channel Receive Data Strobe  46 CHAN_RX_STRB Input Frame synchronization pulse for A/D data. Should be connected to CODEC_TX_STRB  47 CODEC_TX_STRB Input Frame synchronization pulse for D/A data. Should be connected to CODEC_TX_STRB                                                                                                                                                                                                                                                                                                                                                                                                            | 72         | RATE_SEL2            | Input         | section 7.2. The coding rates are also selectable using the Control Word interface      |

| VAD_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71         | RATE_SEL1            | Input         | described in section 5.2.4.                                                             |

| ECHOCAN_EN   Input   Echo Canceller Enable Pin. Active HIGH. See Section 7.3. The Echo Canceller can also be enabled/disabled using the Control Word interface as described in section 5.2.9.    Steep En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70         | RATE_SEL0            | Input         |                                                                                         |

| be enabled/disabled using the Control Word interface as described in section 5.2.9.  83 SLEEP_EN Input Standard Sleep Enable Pin. Active HIGH. See Section 7.6.1.  82 SLIP_EN Input Slip Control Enable Pin. Active HIGH. See Section 7.7.  68 X2/CLKIN Input Clock Input 1. 16.384 Mhz input. See Section 3.3  67 X1 Input AMBE-2000™ Reset pin. Active LOW. See Section 3.3  69 RESETN Input AMBE-2000™ Reset pin. Active LOW. See Section 3.3  20 EPR Output Encode Packet Ready: Following a reset, this signal will have a high to low transition to indicate the first packet is ready. The next packet will be ready approximately 20 msee later. See Note 1.  80 BAUD_SEL0 Input Baud Rate Selector for unframed serial mode See Table 4-B.  81 BAUD_SEL1 Input Channel Receive Data to AMBE-2000™  42 CHAN_RX_DATA Input Channel Transmit Data from AMBE-2000™  28 CHAN_RX_CLK Input Channel Receive Clock  34 CHAN_TX_CLK Input Channel Transmit Clock  35 CHAN_RX_STRB Input Channel Receive Data Strobe  CHAN_RX_STRB Input Channel Receive Data Strobe  CODEC_RX_STRB Input Frame synchronization pulse for A/D data. Should be connected to CODEC_RX_STRB  170 CODEC_TX_STRB Input Frame synchronization pulse for D/A data. Should be connected to CODEC_RX_STRB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86         | VAD_EN               | Input         |                                                                                         |

| SLIP_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78         | ECHOCAN_EN           | Input         |                                                                                         |

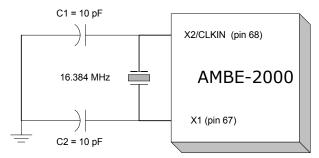

| Clock Input   Clock Input   1. 16.384 Mhz input. See Section 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83         | SLEEP_EN             | Input         | Standard Sleep Enable Pin. Active HIGH. See Section 7.6.1.                              |

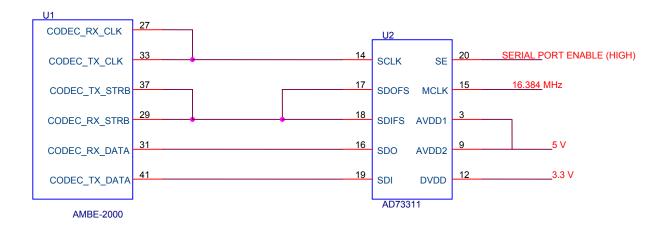

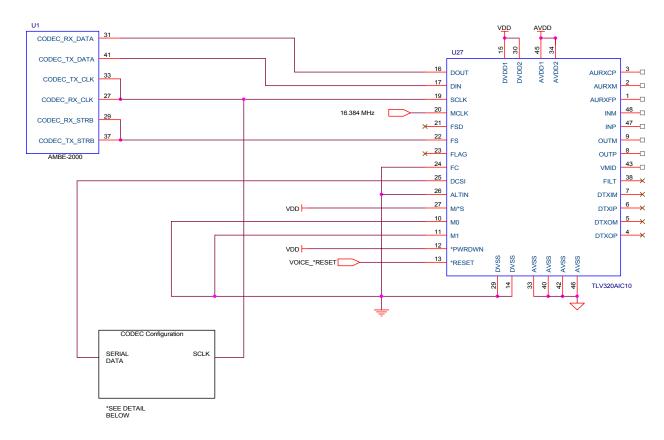

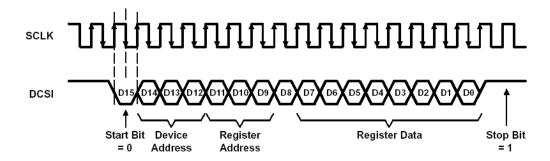

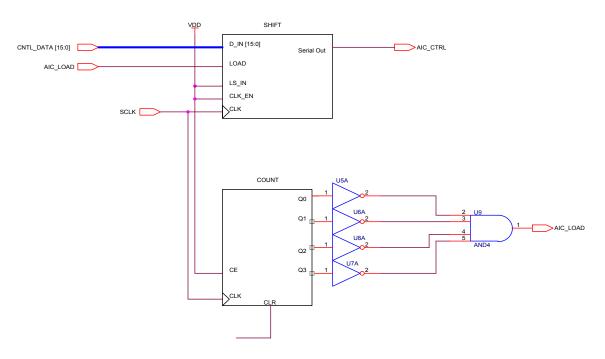

| Output from internal oscillator for the crystal. If the internal oscillator is not used this pin should be unconnected.    AMBE-2000TM Reset pin. Active LOW. See Section 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82         | SLIP_EN              | Input         | Slip Control Enable Pin. Active HIGH. See Section 7.7.                                  |